STC53C Series – 5.0MM X 3.2MM Ceramic SMD 4 Pad CMOS (VC)TCXO

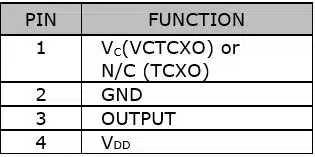

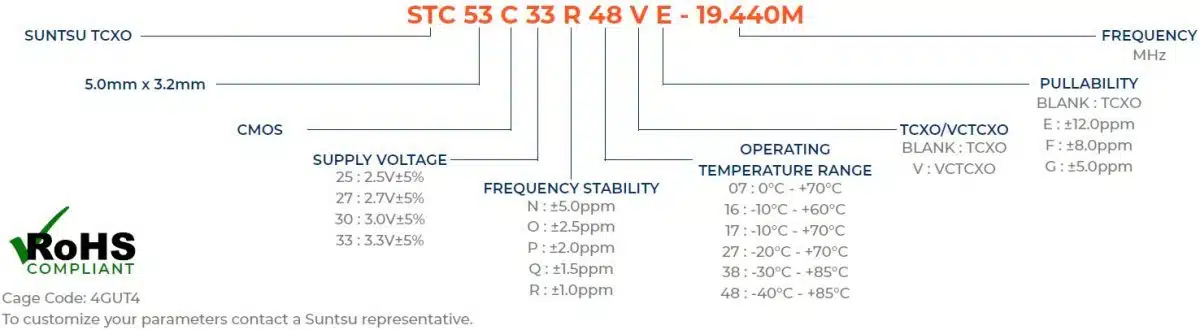

Part Numbering Guide

Electrical Parameters

| Parameters | Units | Min | Typical | Max | Remarks |

|---|---|---|---|---|---|

| Frequency Range | MHz | 6 | 40 | ||

| Frequency Tolerance at +25ºC | ppm | -1.5 | +1.5 | 1 hour after reflow | |

| Freq. Stability vs. Op Temp. | ppm | -1.0 | +1.0 | See part numbering guide for options. | |

| Freq. Stability vs. Supply Voltage | ppm | -0.3 | +0.3 | ±5% Change | |

| Freq. Stability vs. Load | ppm | -0.3 | +0.3 | ±5% Change | |

| Freq. Stability vs. Aging/Year | ppm | -1.0 | +1.0 | 1 year | |

| Operating Temperature | °C | -40 | +85 | See part numbering guide for options. | |

| Storage Temperature | °C | -55 | +125 | ||

| Supply Voltage (VDD) | V | 3.135 | 3.3 | 3.465 | See part numbering guide for options. |

| Current (IDD) | mA | 6 | |||

| Current Voltage (VC, VCTCXO) | V | 0*VDD | VDD | Center Voltage: VDD*50% | |

| Pullability (VCTCXO) | ppm | ±5.0 | ±12.0 | See part numbering guide for options. | |

| Linearity (VCTCXO) | % | 10 | |||

| Output Load (CMOS) | pF | 15 | |||

| Output Logic HIGH Level (VOH) | V | 0.8*VDD | |||

| Output Logic LOW Level (VOL) | V | 0.5*VDD | |||

| Rise (TR) And Fall (TF) Time | ns | 5 | |||

| Symmetry (Duty Cycle) | % | 40 | 50 | 60 | |

| Start-Up Time | ms | 5 | |||

| VC Input Impedance (VCTCXO) | kΩ | 100 | |||

| Phase Noise (Typical) 10Hz Offset | dBc/Hz | -85 | |||

| Phase Noise (Typical) 100Hz Offset | dBc/Hz | -115 | |||

| Phase Noise (Typical) 1KHz Offset | dBc/Hz | -135 | |||

| Phase Noise (Typical) 10KHz Offset | dBc/Hz | -145 | |||

| Phase Noise (Typical) 100KHz Offset | dBc/Hz | -150 |

Outline Drawing & Recommended Landed Pattern

All dimensions are in millimeters (mm) unless otherwise noted. Drawings are not to scale.