5SGSMD4K2F40C2L

| Part Description |

Stratix® V GS Field Programmable Gate Array (FPGA) IC 696 19456000 360000 1517-BBGA, FCBGA |

|---|---|

| Quantity | 1,564 Available (as of May 5, 2026) |

| Product Category | Field Programmable Gate Array (FPGA) |

|---|---|

| Manufacturer | Intel |

| Manufacturing Status | Obsolete |

| Manufacturer Standard Lead Time | RFQ |

| Datasheet |

Specifications & Environmental

| Device Package | 1517-FBGA (40x40) | Grade | Commercial | Operating Temperature | 0°C – 85°C | ||

|---|---|---|---|---|---|---|---|

| Package / Case | 1517-BBGA, FCBGA | Number of I/O | 696 | Voltage | 820 mV - 880 mV | ||

| Mounting Method | Surface Mount | RoHS Compliance | RoHS Compliant | REACH Compliance | REACH Unknown | ||

| Moisture Sensitivity Level | 3 (168 Hours) | Number of LABs/CLBs | 135840 | Number of Logic Elements/Cells | 360000 | ||

| Number of Gates | N/A | ECCN | 3A001A2C | HTS Code | 8542.39.0001 | ||

| Qualification | N/A | Total RAM Bits | 19456000 |

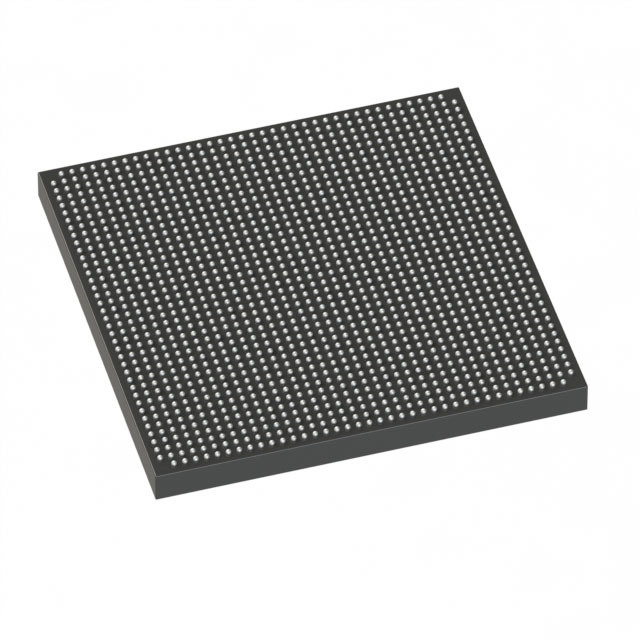

Overview of 5SGSMD4K2F40C2L – Stratix V GS FPGA, 360000 logic elements, 696 I/O, 1517‑FBGA (40×40)

The 5SGSMD4K2F40C2L is a Stratix® V GS field programmable gate array (FPGA) provided in a 1517‑FBGA (40×40) package for surface-mount applications. As a member of the Stratix V family, the GS variant targets transceiver‑based, DSP‑centric designs and combines a high logic element count with substantial embedded memory and DSP resources.

This device suits data‑intensive and high‑precision digital signal processing applications that require large I/O capacity and integrated high‑speed transceiver capability, while operating within a commercial temperature range and low core voltage.

Key Features

- High Logic Density — 360,000 logic elements to implement large-scale combinational and sequential logic functions.

- Embedded Memory — Approximately 19.456 Mbits of on‑chip RAM (19,456,000 total RAM bits) for buffering, packet processing, and DSP intermediate storage.

- DSP Resources — GS‑class Stratix V devices support abundant variable‑precision DSP blocks, with up to 3,926 18×18 or 1,963 27×27 multipliers available for high‑performance arithmetic and filtering operations.

- Integrated Transceivers — GS devices include integrated transceivers with 14.1‑Gbps data‑rate capability suitable for backplane and optical interfaces.

- Extensive I/O — 696 user I/Os to support wide parallel buses, multiple high‑speed interfaces, and complex mezzanine connectivity.

- Package & Mounting — 1517‑BBGA (FCBGA) package in a 40×40 form factor; surface‑mount package suitable for compact board layouts.

- Low Core Voltage — Core supply specified between 820 mV and 880 mV, enabling low‑voltage operation.

- Commercial Grade — Rated for 0 °C to 85 °C operating temperature; RoHS compliant.

- Hard IP and ASIC Path — Stratix V family includes Embedded HardCopy Blocks and a documented low‑risk path to HardCopy V ASICs for production scaling and hardening of instantiated IP.

Typical Applications

- High‑Performance DSP Systems — Use the abundant DSP multipliers and large embedded memory to implement complex filters, transforms, and real‑time signal processing pipelines.

- Optical and Backplane Interfaces — Integrated 14.1‑Gbps transceivers and wide I/O work well for 40G/100G transport, backplane aggregation, and high‑speed serial links.

- Network and Packet Processing — Large logic capacity and significant on‑chip RAM support packet classification, traffic management, and custom network offload functions.

- Broadcast and Military Communications — DSP‑centric architecture and high channel density make the device suitable for modulation, encoding/decoding, and signal conditioning tasks used in broadcast and secure communications equipment.

Unique Advantages

- Large, Integrable Logic Fabric: 360,000 logic elements enable consolidation of multiple functions into a single FPGA, reducing component count and board complexity.

- Significant On‑Chip Memory: Approximately 19.456 Mbits of embedded RAM reduce external memory dependence and lower system latency for buffering and real‑time processing.

- DSP‑Oriented Architecture: Support for thousands of multipliers allows high‑precision, high‑throughput arithmetic operations without extensive external accelerators.

- High I/O Bandwidth: 696 I/Os provide flexibility for connecting wide parallel interfaces, multiple transceiver lanes, and diverse mezzanine modules.

- Commercial Temperature and RoHS Compliance: Rated for 0 °C to 85 °C operation and RoHS compliant for mainstream electronic applications and regulatory compatibility.

- Production Scalability: Family features include Embedded HardCopy Blocks and a HardCopy V ASIC migration path for projects that require a low‑risk route to higher‑volume production.

Why Choose 5SGSMD4K2F40C2L?

The 5SGSMD4K2F40C2L combines high logic density, extensive embedded memory, and DSP‑focused resources within a compact 1517‑FBGA package to address demanding signal‑processing and high‑bandwidth applications. Its 696 I/Os and GS‑class transceiver capability offer designers the flexibility to implement complex multi‑lane interfaces and computationally intensive data paths on a single device.

Engineers and system designers seeking a commercial‑grade FPGA with a clear production scaling path will find this Stratix V GS device aligned with projects that require substantial on‑chip resources, integrated transceiver support, and documentation for migrating hardened IP to ASIC in higher volumes.

Request a quote or submit an inquiry to receive pricing and availability information for the 5SGSMD4K2F40C2L. Our team can provide technical details and lead‑time estimates to support your design and procurement timelines.

Date Founded: 1968

Headquarters: Santa Clara, California, USA

Employees: 130,000+

Revenue: $54.23 Billion

Certifications and Memberships: ISO9001:2015, ISO14001:2015, ISO17025:2017, ISO27001:2022, ISO45001:2018, ISO50001:2018