MT48LC2M32B2TG-7:G TR

| Part Description |

IC DRAM 64MBIT PAR 86TSOP II |

|---|---|

| Quantity | 624 Available (as of May 5, 2026) |

| Product Category | Memory |

|---|---|

| Manufacturer | Micron Technology Inc. |

| Manufacturing Status | Obsolete |

| Manufacturer Standard Lead Time | RFQ |

| Datasheet |

Specifications & Environmental

| Device Package | 86-TSOP II | Memory Format | DRAM | Technology | SDRAM | ||

|---|---|---|---|---|---|---|---|

| Memory Size | 64 Mbit | Access Time | 5.5 ns | Grade | Commercial | ||

| Clock Frequency | 143 MHz | Voltage | 3V ~ 3.6V | Memory Type | Volatile | ||

| Operating Temperature | 0°C ~ 70°C (TA) | Write Cycle Time Word Page | 14 ns | Packaging | 86-TFSOP (0.400", 10.16mm Width) | ||

| Mounting Method | Volatile | Memory Interface | Parallel | Memory Organization | 2M x 32 | ||

| Moisture Sensitivity Level | 2 (1 Year) | RoHS Compliance | RoHS non-compliant | REACH Compliance | REACH Unaffected | ||

| Qualification | N/A | ECCN | EAR99 | HTS Code | 8542.32.0002 |

Overview of MT48LC2M32B2TG-7:G TR – IC DRAM 64Mbit SDRAM, 86‑TSOP II

The MT48LC2M32B2TG-7:G TR is a 64 Mbit (2M × 32) synchronous DRAM (SDR SDRAM) device supplied in an 86‑pin TSOP II package. It provides a parallel memory interface optimized for systems requiring PC100‑class SDRAM operation with programmable burst modes and internal bank management.

Designed for commercial temperature operation (0°C to +70°C) and a single 3.3 V power domain (3.0 V to 3.6 V), this device targets designs that need predictable synchronous memory timing, compact TSOP packaging, and standard SDRAM control features.

Key Features

- Core / Architecture 2M × 32 organization (512K × 32 × 4 banks) providing 64 Mbit of SDRAM with internal pipelined operation and four internal banks for improved row access/precharge management.

- SDR SDRAM Compliance PC100‑compliant, fully synchronous operation with all signals registered on the positive clock edge and support for CAS latency values of 1, 2, and 3.

- Programmable Burst & Access Programmable burst lengths (1, 2, 4, 8, or full page) and column address changes supported every clock cycle to enable flexible data transfer patterns.

- Timing & Performance Target clock frequency 143 MHz (‑7 speed grade) with an access time listed at 5.5 ns and a write cycle time (word/page) of 14 ns; timing grades and CL options are documented in the device specification.

- Refresh & Power Management Auto refresh and self‑refresh capability, including 4096‑cycle refresh modes (64 ms / 4096 cycles for commercial), and support for auto precharge to simplify refresh handling.

- Electrical & I/O LVTTL‑compatible inputs and outputs with a single 3.3 V ±0.3 V supply range (specified 3.0 V to 3.6 V) for standard system integration.

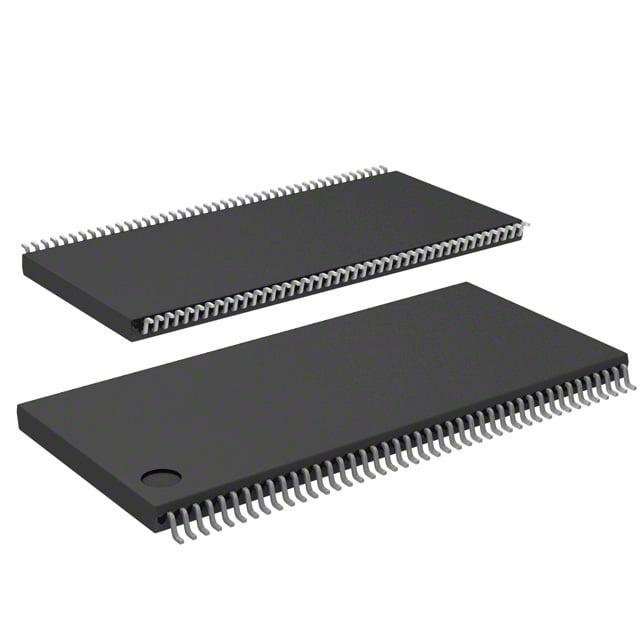

- Package & Temperature 86‑TFSOP / 86‑TSOP II (400 mil, 0.400" / 10.16 mm width) plastic package with commercial operating temperature range of 0°C to +70°C.

Typical Applications

- PC and legacy memory systems PC100‑compliant SDRAM operation makes the device suitable for systems designed to interface with PC‑class synchronous memory timing.

- Embedded systems with parallel SDRAM interface Compact 86‑pin TSOP II packaging and standard LVTTL I/O support direct integration where a parallel SDRAM is required.

- Networking and telecom equipment Four internal banks, programmable bursts, and auto refresh capabilities support streaming and buffer memory tasks in synchronous systems.

Unique Advantages

- Standard SDRAM timing and compatibility: PC100 compliance and support for CAS latencies 1–3 enable operation with established synchronous memory controllers.

- Flexible burst modes: Programmable burst lengths (1, 2, 4, 8, full page) let designers optimize transfers for bursty or sequential workloads.

- Simplified refresh management: Auto refresh and self‑refresh support reduce external refresh handling, easing controller design.

- Single 3.3 V supply: Operates from 3.0 V to 3.6 V, matching common system power rails for straightforward integration.

- Compact TSOP II package: 86‑pin TSOP II (400 mil / 10.16 mm width) offers a space‑efficient footprint for board designs requiring surface‑mount SDRAM.

- Commercial temperature rating: Specified for 0°C to +70°C operation for use in standard commercial environments.

Why Choose IC DRAM 64MBIT PAR 86TSOP II?

The MT48LC2M32B2TG-7:G TR combines a standard PC100‑class SDR SDRAM architecture with a compact 86‑pin TSOP II package, delivering predictable synchronous memory behavior and flexible burst capabilities for parallel SDRAM applications. Its support for multiple CAS latencies, internal bank structure, and single 3.3 V supply make it suitable for designs that require straightforward integration with existing system memory controllers.

This device is appropriate for designers and procurement teams targeting commercial‑temperature systems that need 64 Mbit of parallel SDRAM in a small footprint, with documented timing grades and refresh management features to support reliable system memory operation.

To request a quote or submit a pricing inquiry for the MT48LC2M32B2TG-7:G TR, please provide your quantity and delivery requirements and a representative will respond with availability and pricing details.