5SEEBH40C3N

| Part Description |

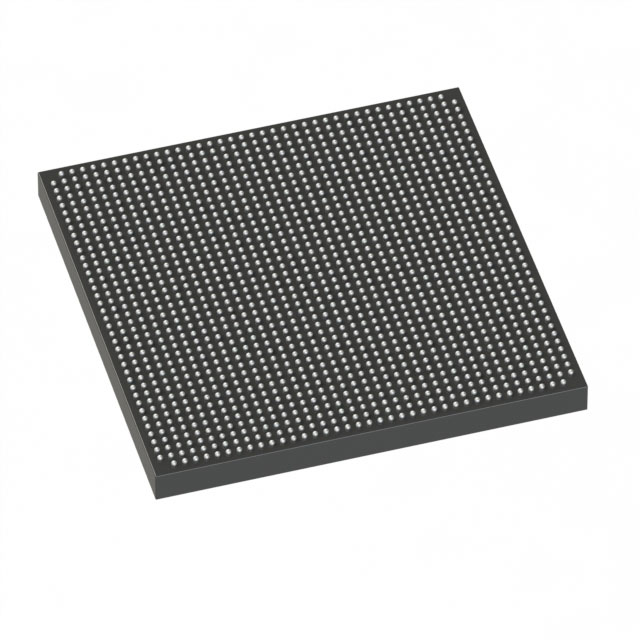

Stratix® V E Field Programmable Gate Array (FPGA) IC 696 53248000 952000 1517-BBGA, FCBGA |

|---|---|

| Quantity | 927 Available (as of May 5, 2026) |

| Product Category | Field Programmable Gate Array (FPGA) |

|---|---|

| Manufacturer | Intel |

| Manufacturing Status | Obsolete |

| Manufacturer Standard Lead Time | RFQ |

| Datasheet |

Specifications & Environmental

| Device Package | 1517-HBGA (45x45) | Grade | Commercial | Operating Temperature | 0°C – 85°C | ||

|---|---|---|---|---|---|---|---|

| Package / Case | 1517-BBGA, FCBGA | Number of I/O | 696 | Voltage | 820 mV - 880 mV | ||

| Mounting Method | Surface Mount | RoHS Compliance | RoHS Compliant | REACH Compliance | REACH Unknown | ||

| Moisture Sensitivity Level | 3 (168 Hours) | Number of LABs/CLBs | 359250 | Number of Logic Elements/Cells | 952000 | ||

| Number of Gates | N/A | ECCN | 3A001A2C | HTS Code | 8542.39.0001 | ||

| Qualification | N/A | Total RAM Bits | 53248000 |

Overview of 5SEEBH40C3N – Stratix® V E Field Programmable Gate Array (FPGA) IC

The 5SEEBH40C3N is a Stratix V E field programmable gate array offering a high logic density FPGA fabric built on the Stratix V architecture. It combines a large number of logic elements, abundant embedded memory, and extensive I/O to address designs that require substantial programmable logic capacity and system integration.

This device is suited for applications such as ASIC and system emulation, diagnostic imaging, and instrumentation where nearly one million logic elements, significant on‑chip memory, and broad I/O count are required. The device is supplied in a 1517‑BBGA FCBGA package for surface-mount assembly and is specified for commercial temperature operation.

Key Features

- Logic Capacity Provides 952,000 logic elements for implementing large-scale programmable logic and complex system functions.

- Embedded Memory Approximately 53 Mbits of on-chip RAM (total RAM bits: 53,248,000) using Stratix V memory architecture including M20K memory blocks.

- I/O Density Up to 696 device I/Os to support wide parallel interfaces, board-level connectivity, and dense signal routing.

- DSP and Hard IP Includes variable precision DSP resources and integrated hard IP blocks; the family also supports an Embedded HardCopy Block for hardening IP such as PCIe generations.

- Transceiver and Fabric Technology Stratix V family innovations include integrated transceivers (family-level capability up to 28.05 Gbps) and an adaptive logic module (ALM) based fabric with multi-track routing.

- Process and Clocking Built on 28‑nm process technology with fractional PLLs and a comprehensive fabric clocking network for flexible timing architectures.

- Power Supply Specified core voltage range of 820 mV to 880 mV to match system power-rail requirements.

- Package & Mounting 1517‑BBGA (FCBGA) / supplier package 1517‑HBGA (45×45) in a surface-mount form factor for high-density board integration.

- Operating Range & Compliance Commercial grade operation from 0 °C to 85 °C; RoHS compliant.

Typical Applications

- ASIC and System Emulation Use the 952,000 logic elements and extensive memory to prototype, validate, or emulate large ASIC designs and complex SoCs.

- Diagnostic Imaging Leverage abundant DSP resources and on-chip memory for real-time image processing pipelines and high-throughput data handling.

- Instrumentation High I/O count and programmable logic capacity enable custom measurement, control, and data-aggregation systems for lab and industrial instruments.

- High‑bandwidth Transport and Processing Family features such as integrated transceivers and hardened IP blocks support bandwidth‑centric data transport and protocol processing tasks.

Unique Advantages

- Large Programmable Fabric: 952,000 logic elements provide the headroom to implement complex logic, datapaths, and system-level functions without partitioning across multiple devices.

- Substantial On‑chip Memory: Approximately 53 Mbits of embedded RAM reduce external memory dependence and simplify board-level BOM and routing.

- High I/O Count: 696 I/Os enable dense peripheral and bus connections, simplifying integration with multi-channel front ends and parallel interfaces.

- Family-Level Hard IP and DSP: Integrated hard IP blocks and variable precision DSP resources allow efficient implementation of compute- and protocol-intensive functions.

- Commercial Temperature and RoHS Compliance: Specified 0 °C to 85 °C operation and RoHS compliance support standard commercial deployments and manufacturing requirements.

- Compact Surface-Mount Package: 1517‑BBGA (45×45 HBGA footprint) provides a high-density package option for space-constrained PCBs.

Why Choose 5SEEBH40C3N?

The 5SEEBH40C3N is positioned for designs that demand a large programmable fabric, extensive on-chip memory, and high I/O density in a commercial-grade, surface-mount package. Its Stratix V architecture delivers a combination of logic, memory, DSP, and family-level hard IP capabilities that simplify implementing complex algorithms and protocol handling on a single device.

This part is appropriate for engineering teams building emulation platforms, imaging systems, instrumentation, and other data- or logic‑intensive applications that require a high logic element count, substantial embedded RAM, and broad connectivity while adhering to commercial temperature and RoHS manufacturing constraints.

If you would like pricing, availability, or a technical quotation for 5SEEBH40C3N, submit a request for a quote or an inquiry and our team will respond with the requested details.

Date Founded: 1968

Headquarters: Santa Clara, California, USA

Employees: 130,000+

Revenue: $54.23 Billion

Certifications and Memberships: ISO9001:2015, ISO14001:2015, ISO17025:2017, ISO27001:2022, ISO45001:2018, ISO50001:2018