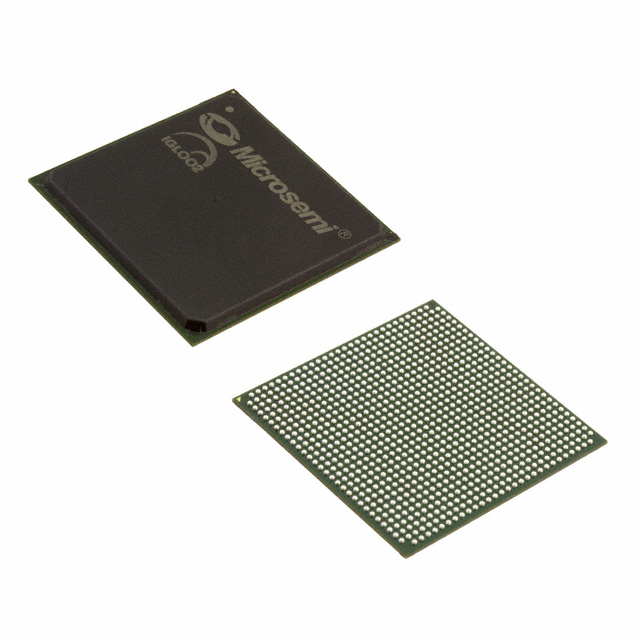

M2GL050-1FGG484

| Part Description |

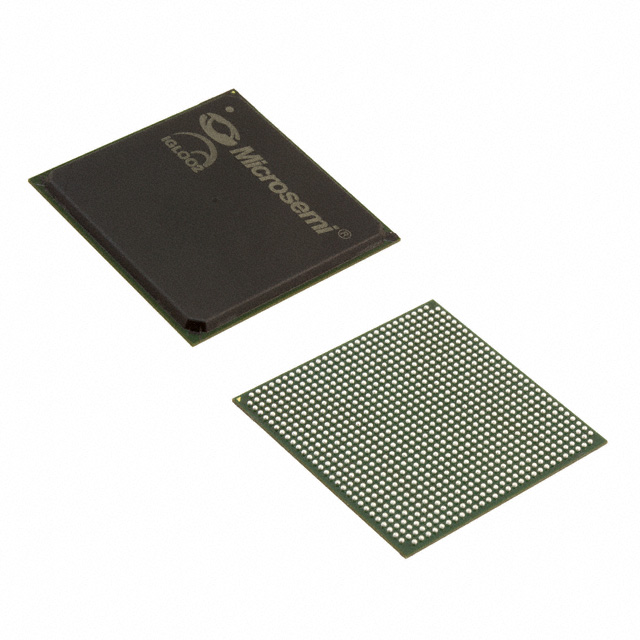

IGLOO2 Field Programmable Gate Array (FPGA) IC 267 1869824 56340 484-BGA |

|---|---|

| Quantity | 283 Available (as of May 5, 2026) |

| Product Category | Field Programmable Gate Array (FPGA) |

|---|---|

| Manufacturer | Microchip Technology |

| Manufacturing Status | Active |

| Manufacturer Standard Lead Time | 16 Weeks |

| Datasheet |

Specifications & Environmental

| Device Package | 484-FPBGA (23x23) | Grade | Commercial | Operating Temperature | 0°C – 85°C | ||

|---|---|---|---|---|---|---|---|

| Package / Case | 484-BGA | Number of I/O | 267 | Voltage | 1.14 V - 2.625 V | ||

| Mounting Method | Surface Mount | RoHS Compliance | ROHS3 Compliant | REACH Compliance | REACH Unaffected | ||

| Moisture Sensitivity Level | 3 (168 Hours) | Number of LABs/CLBs | 56340 | Number of Logic Elements/Cells | 56340 | ||

| Number of Gates | N/A | ECCN | 3A991D | HTS Code | 8542.39.0001 | ||

| Qualification | N/A | Total RAM Bits | 1869824 |

Overview of M2GL050-1FGG484 – IGLOO2 FPGA, 56,340 Logic Elements, 267 I/Os, 484-BGA

The M2GL050-1FGG484 is an IGLOO2 field programmable gate array (FPGA) integrating flash-based FPGA fabric with high-performance communications and memory interfaces. It targets low-power, secure programmable logic applications where a combination of substantial logic capacity, abundant I/O and advanced serial/memory interfaces is required.

Built on IGLOO2 architecture, the device combines 56,340 logic elements, approximately 1.87 Mbits of on-chip RAM, high-speed SERDES and DDRx memory controller capabilities, making it suitable for designs that require DSP acceleration, fast connectivity and embedded memory bandwidth within a commercial temperature range.

Key Features

- Core and Logic 56,340 logic elements implemented with efficient 4-input LUT fabric and carry chains for compact logic and arithmetic implementations.

- On-Chip Memory Approximately 1.87 Mbits of total on-chip RAM. Series-level memory resources include 64 KB embedded SRAM and up to 512 KB embedded nonvolatile memory (eNVM) for configuration and data buffering.

- DSP and Math Blocks Series supports embedded mathblocks for DSP, with up to 240 fast mathblocks capable of 18×18 signed multiplication and a 44-bit accumulator for signal processing tasks.

- High-Speed Serial Interfaces Up to 16 SERDES lanes with native SERDES support and XGXS/XAUI extension. Includes PCI Express endpoint controller options (x1, x2, x4) for high-bandwidth peripheral connectivity.

- High-Speed Memory Interfaces Up to two DDRx memory controllers supporting LPDDR/DDR2/DDR3 with maximum 333 MHz clock rate and multiple DRAM bus width modes to support high-throughput external memory.

- Clocking and Timing Multiple clock sources and up to eight Clock Conditioning Circuits (CCCs) with integrated analog PLLs; frequency handling spans input 1–200 MHz and output 20–400 MHz for flexible timing architectures.

- I/O and Voltage 267 user I/Os supporting multi-standard I/O signaling (LVCMOS, LVTTL, DDR standards, LVDS variants, and more) and a supply range of 1.14 V to 2.625 V; core voltage 1.2 V.

- Security Design security features available across the family, including encrypted bitstream loading, device certificate support and anti-tamper capabilities; data security primitives such as AES-256, SHA-256, ECC and PUF key support are available on premium devices.

- Package and Temperature Surface-mount 484-ball FPBGA package (23 × 23 mm) and commercial operating temperature range of 0 °C to 85 °C.

- Reliability and Power Flash-based configuration and architecture designed for low standby power and predictable configuration behavior suitable for power-sensitive designs.

Typical Applications

- High-Performance Communications Implement serial PHYs, protocol bridges and PCIe endpoints using the integrated SERDES lanes and PCIe endpoint controller support.

- Embedded DSP and Signal Processing Use the mathblocks and on-chip memory for FIR filters, FFT front ends or mixed-signal processing pipelines that require compact, hardware-accelerated arithmetic.

- Memory Interface Controllers Deploy DDR2/DDR3 memory controllers to manage external DRAM for buffering, frame storage or high-throughput data acquisition systems.

- Secure Embedded Systems Leverage design and data security features for devices that need encrypted bitstreams, secure key storage and anti-tamper protections.

Unique Advantages

- Substantial Logic Capacity: 56,340 logic elements provide a large fabric for complex glue logic, accelerators or system-on-chip integration without splitting across multiple devices.

- Integrated High-Speed Interfaces: Native SERDES and PCIe endpoint capabilities reduce external interface components and simplify high-bandwidth link designs.

- Flexible Memory Subsystem: On-chip SRAM and eNVM combined with DDRx controllers enable a layered memory architecture for low-latency on-chip storage and high-capacity off-chip DRAM.

- Security Options: Built-in design security features and optional data-security primitives support protected IP and secure boot/load models.

- Commercial Temperature Suitability: Rated for 0 °C to 85 °C, meeting requirements for a wide range of commercial and enterprise applications.

- Compact, Surface-Mount Packaging: 484-ball FPBGA in a 23 × 23 mm footprint supports high I/O density in space-constrained PCB layouts.

Why Choose M2GL050-1FGG484?

The M2GL050-1FGG484 delivers a combination of sizable logic resources, flexible I/O and advanced communications and memory interfaces within a flash-based IGLOO2 architecture. Its blend of on-chip memory, DSP mathblocks and SERDES lanes makes it suitable for designers building compact, secure and performance-oriented programmable logic solutions in commercial-temperature applications.

This device is well suited for engineering teams that need integrated serial connectivity, DDRx memory support and security features while maintaining a focus on power and predictable configuration behavior. The IGLOO2 family-level resources such as multiple clock conditioning circuits, DMA engines and memory controller options provide scalability and integration that help reduce system BOM and simplify board-level design.

Request a quote or submit an inquiry to receive pricing and availability information for the M2GL050-1FGG484.

Date Founded: 1989

Headquarters: Chandler, Arizona, USA

Employees: 22,000+

Revenue: $8.349 Billion

Certifications and Memberships: ISO9001:2015, IATF16949:2016, AS 9100D