EP20K200CF484C7ES

| Part Description |

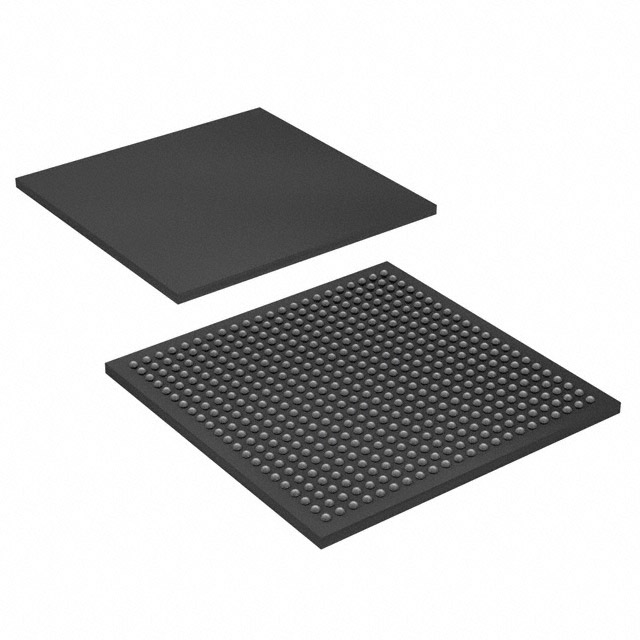

APEX-20KC® Field Programmable Gate Array (FPGA) IC 376 106496 8320 484-BBGA |

|---|---|

| Quantity | 1,164 Available (as of May 5, 2026) |

| Product Category | Field Programmable Gate Array (FPGA) |

|---|---|

| Manufacturer | Intel |

| Manufacturing Status | Obsolete |

| Manufacturer Standard Lead Time | RFQ |

| Datasheet |

Specifications & Environmental

| Device Package | 484-FBGA (23x23) | Grade | Commercial | Operating Temperature | 0°C – 85°C | ||

|---|---|---|---|---|---|---|---|

| Package / Case | 484-BBGA | Number of I/O | 376 | Voltage | 1.71 V - 1.89 V | ||

| Mounting Method | Surface Mount | RoHS Compliance | Unknown | REACH Compliance | REACH Unknown | ||

| Moisture Sensitivity Level | 3 (168 Hours) | Number of LABs/CLBs | 832 | Number of Logic Elements/Cells | 8320 | ||

| Number of Gates | 526000 | ECCN | OBSOLETE | HTS Code | 0000.00.0000 | ||

| Qualification | N/A | Total RAM Bits | 106496 |

Overview of EP20K200CF484C7ES – APEX-20KC® Field Programmable Gate Array (FPGA) IC 376 I/Os, 106,496 RAM bits, 8,320 logic elements, 484‑BBGA

The EP20K200CF484C7ES is an APEX‑20KC series FPGA offering a high‑density, low‑power programmable logic solution in a 484‑BBGA package. Built on the APEX 20KC architecture, this device delivers a compact combination of logic, embedded memory and I/O resources suitable for mid‑range embedded systems and commercial applications that require flexible hardware customization.

Key value comes from its integrated logic resources and memory, predictable interconnect and MultiVolt I/O capability, enabling implementation of custom control, interface and data‑path functions with a single programmable device.

Key Features

- Logic Capacity — 8,320 logic elements (LEs) and up to 526,000 system gates provide the programmable fabric for implementing control, datapath and glue logic.

- Embedded Memory — Approximately 0.106 Mbits of on‑chip RAM (106,496 bits) for FIFOs, buffers and small data structures without consuming LE resources.

- I/O and Package — 376 user I/O pins in a 484‑BBGA surface‑mount package (supplier package: 484‑FBGA, 23 × 23); suitable for dense I/O routing in compact boards.

- Clock and Timing — Device family supports flexible clock management; this specific device offers up to 2 PLLs for clock synthesis and phase management (as defined for the EP20K200C device).

- Process and Interconnect — APEX 20KC architecture implemented using a 0.15‑μm copper‑metal process for improved performance and reduced power compared to previous generations.

- Supply and Power — Internal supply centered at 1.8 V (typical); product specification lists an allowable internal voltage range of 1.71 V to 1.89 V and MultiVolt I/O support for standard interface voltages.

- Operating Range — Commercial grade device rated for 0 °C to 85 °C operation.

- Design Ecosystem — Supported by APEX 20KC series design flows and megafunction libraries for rapid implementation and automatic place‑and‑route (as provided by the series documentation).

Typical Applications

- Industrial Control — Implement real‑time control logic, interface bridging and custom protocol handling where compact, reprogrammable hardware is required.

- Communications and Networking — Provide protocol processing, I/O aggregation and timing control using the device’s ample I/O and embedded memory resources.

- Storage and Memory Interfaces — Implement buffering, FIFO control and custom memory controllers leveraging on‑chip RAM and dedicated interconnect chains.

- Embedded System Integration — Replace multiple discrete components by consolidating glue logic, peripheral interfaces and custom functions into a single programmable device.

Unique Advantages

- High‑density programmable fabric: 8,320 logic elements and 526,000 gates let you implement substantial logic and control functions on one device, reducing board complexity.

- Integrated on‑chip memory: Approximately 106,496 bits of embedded RAM enable efficient FIFO and buffering without consuming logic elements.

- Broad I/O capability in a compact package: 376 user I/Os in a 484‑BBGA footprint support dense interfacing while keeping board area small.

- Deterministic clocking options: On‑device PLL resources support clock multiplication, division and phase control needed for synchronized subsystems.

- Low‑power copper process: The 0.15‑μm copper‑metal fabrication improves performance and reduces power compared with earlier process nodes used in the same product family.

Why Choose EP20K200CF484C7ES?

The EP20K200CF484C7ES places a balanced mix of logic capacity, embedded memory and high‑pin‑count I/O into a surface‑mount 484‑BBGA package, making it a practical choice for mid‑complexity designs that require reprogrammability and integration. Its APEX‑20KC family heritage brings copper interconnect performance, hierarchical interconnect structure and clock management features that help designers meet timing and integration targets.

This device is suited for engineering teams looking to consolidate discrete logic, implement custom interfaces, or accelerate time‑to‑market through programmable hardware and supported design flows. The commercial temperature rating and defined supply range support deployment in typical commercial embedded environments.

If you would like pricing or availability, request a quote or submit a quote request to receive product and procurement information.

Date Founded: 1968

Headquarters: Santa Clara, California, USA

Employees: 130,000+

Revenue: $54.23 Billion

Certifications and Memberships: ISO9001:2015, ISO14001:2015, ISO17025:2017, ISO27001:2022, ISO45001:2018, ISO50001:2018