EPF6010ATC100-1N

| Part Description |

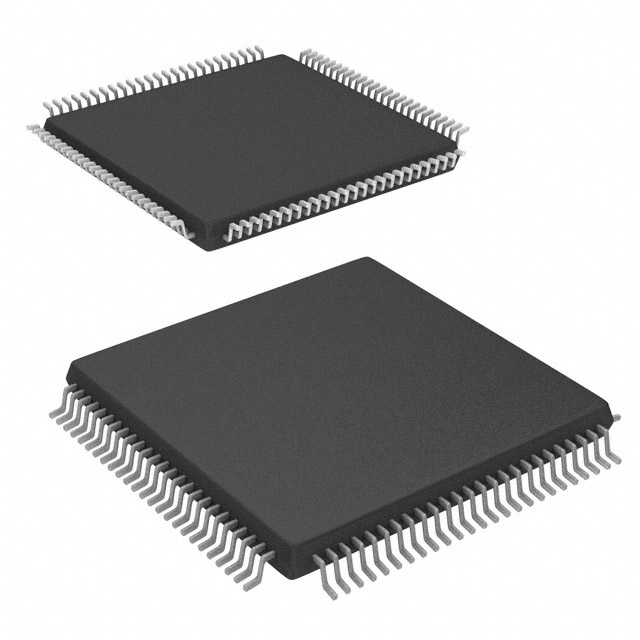

FLEX 6000 Field Programmable Gate Array (FPGA) IC 71 880 100-TQFP |

|---|---|

| Quantity | 154 Available (as of May 5, 2026) |

| Product Category | Field Programmable Gate Array (FPGA) |

|---|---|

| Manufacturer | Intel |

| Manufacturing Status | Obsolete |

| Manufacturer Standard Lead Time | RFQ |

| Datasheet |

Specifications & Environmental

| Device Package | 100-TQFP (14x14) | Grade | Commercial | Operating Temperature | 0°C – 85°C | ||

|---|---|---|---|---|---|---|---|

| Package / Case | 100-TQFP | Number of I/O | 71 | Voltage | 3 V - 3.6 V | ||

| Mounting Method | Surface Mount | RoHS Compliance | Unknown | REACH Compliance | REACH Unaffected | ||

| Moisture Sensitivity Level | 3 (168 Hours) | Number of LABs/CLBs | 88 | Number of Logic Elements/Cells | 880 | ||

| Number of Gates | 10000 | ECCN | 3A991D | HTS Code | 8542.39.0001 | ||

| Qualification | N/A |

Overview of EPF6010ATC100-1N – FLEX 6000 FPGA, 71 I/O, 880 logic elements, 100‑TQFP

The EPF6010ATC100-1N is an Intel FLEX 6000 family field programmable gate array (FPGA) supplied in a 100‑pin TQFP (14×14) package. It implements a register‑rich, look‑up table (LUT) based OptiFLEX architecture with in-circuit reconfigurability, making it suitable as a low‑cost programmable alternative to fixed gate‑array designs and for rapid prototyping and design testing.

This commercial‑grade, surface‑mount device provides 880 logic elements (approximately 10,000 typical gates), 71 user I/O pins, multi‑voltage I/O capability, and a 3.0 V–3.6 V supply range with an operating temperature of 0 °C to 85 °C. It is RoHS compliant.

Key Features

- OptiFLEX LUT‑based architecture Register‑rich, LUT‑based design optimizing device area efficiency for flexible logic implementation.

- Logic capacity 880 logic elements (approximately 10,000 typical gates) to support mid‑density programmable logic functions.

- I/O and interface features 71 I/O pins with individual tri‑state output enable control and programmable output slew‑rate control to manage signal integrity and interfacing.

- FastTrack interconnect and dedicated chains Continuous FastTrack routing structure plus dedicated carry and cascade chains for efficient arithmetic and high‑fan‑in logic implementations.

- Clock and global routing Built‑in low‑skew clock distribution tree with four low‑skew global paths for clock, clear, preset, or logic signals.

- In‑circuit reconfigurability (ICR) Supports reconfiguration via an external configuration device or intelligent controller for field updates and design iteration.

- JTAG boundary‑scan Built‑in IEEE Std. 1149.1 compliant JTAG boundary‑scan circuitry for board‑level test without consuming device logic.

- Package and mounting 100‑pin TQFP (14×14) surface‑mount package suitable for compact PCB designs.

- Supply and temperature Operates from 3.0 V to 3.6 V with a commercial temperature range of 0 °C to 85 °C.

- Regulatory RoHS compliant.

Typical Applications

- Prototyping and design verification Use for rapid iteration during prototype development and functional testing where reprogrammability speeds design changes.

- Low‑volume gate‑array replacement Acts as a cost‑effective programmable alternative to gate‑array implementations in lower production volumes.

- Embedded control and glue logic Implement custom control, interfacing, and glue logic between system components using the device’s flexible I/O and dedicated logic chains.

- Field‑upgradeable systems Leverage in‑circuit reconfiguration to update or modify device behavior in deployed hardware.

Unique Advantages

- Reconfigurability on demand: In‑circuit reconfigurability lets you update logic in the field or iterate quickly during development.

- Efficient arithmetic and logic: Dedicated carry and cascade chains accelerate adders, counters, comparators, and high‑fan‑in logic while simplifying synthesis.

- Predictable timing and routing: FastTrack interconnect and low‑skew global paths provide consistent routing delays and clock distribution for reliable timing closure.

- Board‑level test and debug: Integrated JTAG boundary‑scan simplifies manufacturing test and system debug without consuming user logic resources.

- Compact packaging: 100‑pin TQFP (14×14) surface‑mount package balances pin count and PCB footprint for space‑constrained designs.

Why Choose EPF6010ATC100-1N?

The EPF6010ATC100-1N provides a practical balance of programmable logic capacity and system I/O in a compact TQFP package. Its OptiFLEX architecture, combined with FastTrack interconnect and dedicated arithmetic chains, enables designers to implement mid‑density logic functions with predictable routing and timing behavior.

Ideal for teams needing a reprogrammable, low‑cost alternative to gate arrays or for projects requiring in‑field updates and rapid prototyping, this commercial‑grade FPGA offers a clear specification set—880 logic elements, 71 I/Os, 3.0–3.6 V supply, and 0 °C–85 °C operation—backed by standard FPGA system features like JTAG boundary‑scan and programmable I/O control.

Request a quote or submit a purchase inquiry to receive pricing, availability, and ordering information for the EPF6010ATC100-1N.

Date Founded: 1968

Headquarters: Santa Clara, California, USA

Employees: 130,000+

Revenue: $54.23 Billion

Certifications and Memberships: ISO9001:2015, ISO14001:2015, ISO17025:2017, ISO27001:2022, ISO45001:2018, ISO50001:2018