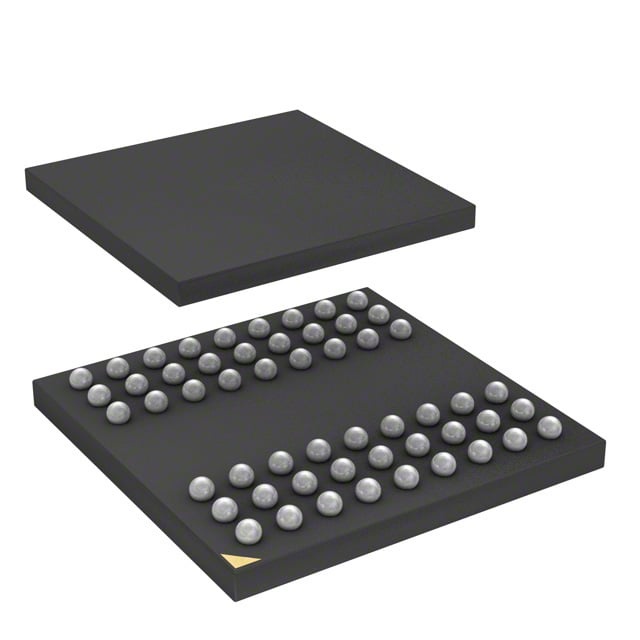

IS45S16160J-6TLA1

| Part Description |

IC DRAM 256MBIT PAR 54TSOP II |

|---|---|

| Quantity | 622 Available (as of May 5, 2026) |

| Product Category | Memory |

|---|---|

| Manufacturer | Integrated Silicon Solution Inc |

| Manufacturing Status | Active |

| Manufacturer Standard Lead Time | 10 Weeks |

| Datasheet |

Specifications & Environmental

| Device Package | 54-TSOP II | Memory Format | DRAM | Technology | SDRAM | ||

|---|---|---|---|---|---|---|---|

| Memory Size | 256 Mbit | Access Time | 5.4 ns | Grade | Industrial | ||

| Clock Frequency | 166 MHz | Voltage | 3V ~ 3.6V | Memory Type | Volatile | ||

| Operating Temperature | -40°C ~ 85°C (TA) | Write Cycle Time Word Page | N/A | Packaging | 54-TSOP (0.400", 10.16mm Width) | ||

| Mounting Method | Volatile | Memory Interface | Parallel | Memory Organization | 16M x 16 | ||

| Moisture Sensitivity Level | 3 (168 Hours) | RoHS Compliance | ROHS Compliant | REACH Compliance | REACH Unaffected | ||

| Qualification | N/A | ECCN | EAR99 | HTS Code | 8542.32.0024 |

Overview of IS45S16160J-6TLA1 – IC DRAM 256MBIT PAR 54TSOP II

The IS45S16160J-6TLA1 is a 256 Mbit volatile DRAM device from ISSI, implemented as SDRAM with a 16M × 16 memory organization and a parallel memory interface. It delivers operation up to a 166 MHz clock with a specified access time of 5.4 ns, and operates from a 3.0 V to 3.6 V supply.

Packaged in a 54‑lead TSOP II (0.400", 10.16 mm width) and rated for an operating temperature range of -40°C to 85°C, this device is targeted at board-level memory applications requiring a parallel SDRAM form factor and defined electrical and thermal envelopes.

Key Features

- Memory Type / Format Volatile DRAM implemented as SDRAM; memory format specified as DRAM and listed as volatile.

- Memory Organization 256 Mbit capacity arranged as 16M × 16, providing a parallel 16‑bit data path.

- Performance Rated for operation at a 166 MHz clock with an access time of 5.4 ns, enabling synchronous parallel access at the specified timing.

- Interface Parallel memory interface suitable for systems designed for parallel SDRAM connectivity.

- Power Supply voltage range of 3.0 V to 3.6 V to match 3 V system rails.

- Package 54‑lead TSOP II package (0.400" / 10.16 mm width) for board-level mounting; supplier device package listed as 54‑TSOP II.

- Operating Temperature Specified operating temperature range of -40°C to 85°C (TA) for extended ambient conditions.

Typical Applications

- Board-level memory expansion Use where a 256 Mbit parallel SDRAM is required for system memory density in a compact TSOP II package.

- Parallel SDRAM systems Integrates into designs that rely on a 16‑bit parallel memory interface and synchronous DRAM timing.

- Industrial-temperature designs Suitable for equipment requiring operation across a -40°C to 85°C temperature range.

- 3 V system designs Intended for applications operating with 3.0 V to 3.6 V supply rails.

Unique Advantages

- Defined SDRAM performance: 166 MHz clock rating and 5.4 ns access time provide clear timing parameters for system design and timing analysis.

- Parallel 16‑bit organization: 16M × 16 arrangement delivers a straightforward 16‑bit data path for legacy or board-level parallel memory architectures.

- Compact TSOP II footprint: 54‑lead TSOP II package (10.16 mm width) enables higher density board layouts while maintaining standard package geometry.

- Wide supply tolerance: 3.0 V to 3.6 V support allows use with common 3 V system rails.

- Extended ambient range: -40°C to 85°C operating range supports deployments in varying environmental conditions.

Why Choose IC DRAM 256MBIT PAR 54TSOP II?

The IS45S16160J-6TLA1 positions itself as a compact, board‑level SDRAM option with explicit electrical and timing specifications—256 Mbit capacity (16M × 16), 166 MHz clock rating, and 5.4 ns access time—packaged in a 54‑lead TSOP II. Its voltage range (3.0 V–3.6 V) and -40°C to 85°C operating window make it suitable for systems that require defined SDRAM behavior within those electrical and thermal constraints.

This device is appropriate for designers and procurement teams specifying parallel SDRAM memory for legacy or new designs that require a 16‑bit parallel interface and a compact TSOP II package. Its clear specification set aids integration, timing validation, and board-level footprint planning.

Request a quote or submit a product inquiry to obtain pricing, lead-time, and availability information for the IS45S16160J-6TLA1.