MT48LC4M16A2B4-6A IT:J TR

| Part Description |

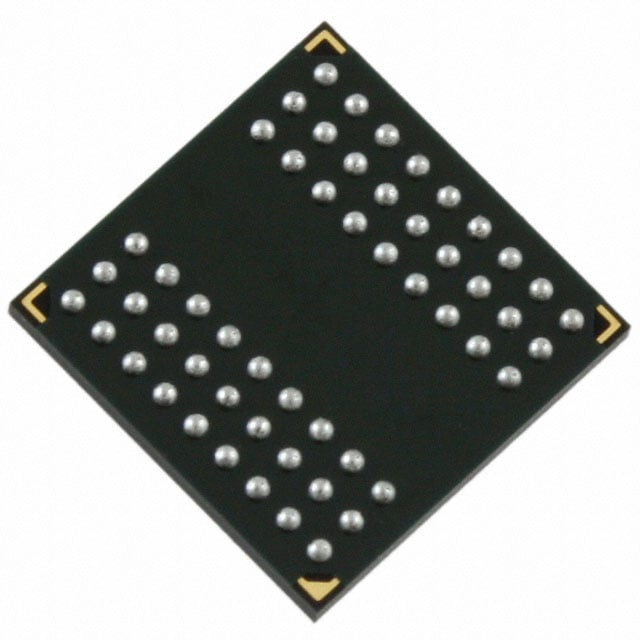

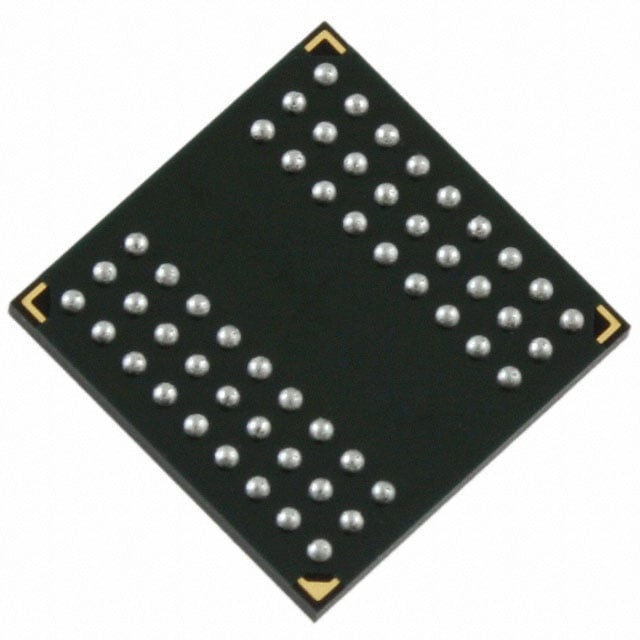

IC DRAM 64MBIT PAR 54VFBGA |

|---|---|

| Quantity | 571 Available (as of May 5, 2026) |

| Product Category | Memory |

|---|---|

| Manufacturer | Micron Technology Inc. |

| Manufacturing Status | Obsolete |

| Manufacturer Standard Lead Time | RFQ |

| Datasheet |

Specifications & Environmental

| Device Package | 54-VFBGA (8x8) | Memory Format | DRAM | Technology | SDRAM | ||

|---|---|---|---|---|---|---|---|

| Memory Size | 64 Mbit | Access Time | 5.4 ns | Grade | Industrial | ||

| Clock Frequency | 167 MHz | Voltage | 3V ~ 3.6V | Memory Type | Volatile | ||

| Operating Temperature | -40°C ~ 85°C (TA) | Write Cycle Time Word Page | 12 ns | Packaging | 54-VFBGA | ||

| Mounting Method | Volatile | Memory Interface | Parallel | Memory Organization | 4M x 16 | ||

| Moisture Sensitivity Level | 3 (168 Hours) | RoHS Compliance | ROHS3 Compliant | REACH Compliance | REACH Unaffected | ||

| Qualification | N/A | ECCN | EAR99 | HTS Code | 8542.32.0002 |

Overview of MT48LC4M16A2B4-6A IT:J TR – 64 Mbit SDRAM (4M × 16), 54‑VFBGA

The MT48LC4M16A2B4-6A IT:J TR is a volatile SDRAM device organized as 4M × 16 for a total capacity of 64 Mbit. It implements fully synchronous SDRAM architecture with a parallel memory interface and is offered in a 54-ball VFBGA package (8 × 8).

Designed for systems that require a parallel SDRAM memory element with industrial temperature operation and support for PC100/PC133-class timing, this device provides standard SDRAM functions and timing options to integrate into synchronous memory subsystems.

Key Features

- Memory Type & Organization 64 Mbit SDRAM organized as 4M × 16 (DRAM, volatile) for parallel memory implementations.

- Performance & Timing Supports a clock frequency up to 167 MHz (speed grade -6A) with documented timing (e.g., CL and RCD values in the datasheet) and an access time of 5.4 ns.

- Burst and Internal Operation Fully synchronous operation with internal, pipelined architecture and programmable burst lengths (BL = 1, 2, 4, 8, or full page) as described in the device family datasheet.

- Refresh & Power Management Auto refresh and self-refresh modes are supported (standard and low-power modes available in device family options) with standard 4096-cycle refresh intervals per device family documentation.

- Voltage & I/O Single-supply operation from 3.0 V to 3.6 V; LVTTL-compatible inputs and outputs are part of the device family feature set.

- Package 54-ball VFBGA package, 8 × 8 mm footprint (54‑VFBGA), suitable for compact board layouts.

- Industrial Temperature Range Rated for operation from −40°C to +85°C (TA), matching the IT industrial grade marking in the part number.

- Write Cycle Word/page write cycle time of 12 ns as specified in product parameters.

Typical Applications

- Parallel SDRAM systems — For designs requiring a 64 Mbit parallel SDRAM (4M × 16) memory device with standard SDRAM control and burst modes.

- Industrial-temperature designs — Suitable for systems that require operation across −40°C to +85°C.

- Compact board-level memory — The 54-ball VFBGA (8 × 8) package supports denser board layouts where a small-footprint DRAM is needed.

Unique Advantages

- Standard SDRAM feature set: Implements fully synchronous, pipelined SDRAM behavior with programmable burst lengths and internal bank architecture, enabling conventional SDRAM control schemes.

- High-frequency operation: Speed grade -6A support at 167 MHz provides timing headroom aligned with PC100/PC133-class family timing documented in the datasheet.

- Industrial temperature rating: −40°C to +85°C operation allows deployment in temperature-sensitive environments.

- Compact VFBGA package: 54-ball 8 × 8 VFBGA reduces PCB area, aiding designs with tight real-estate constraints.

- Standard 3.3 V supply range: 3.0 V to 3.6 V single-supply operation simplifies power rail integration for systems using LVTTL-level signaling.

Why Choose MT48LC4M16A2B4-6A IT:J TR?

The MT48LC4M16A2B4-6A IT:J TR provides a conventional SDRAM solution in a compact VFBGA package with industrial temperature capability and support for PC100/PC133-class timing. Its 4M × 16 organization, parallel interface, and documented timing options make it a straightforward memory element for systems that rely on synchronous DRAM control.

This device is suited for designs prioritizing standard SDRAM functionality, compact package footprint, and operation across an extended temperature range, offering a predictable integration path within established SDRAM memory subsystems.

Request a quote or submit an inquiry to start the procurement process for MT48LC4M16A2B4-6A IT:J TR and discuss availability and lead times.