EP1K10TC144-1N

| Part Description |

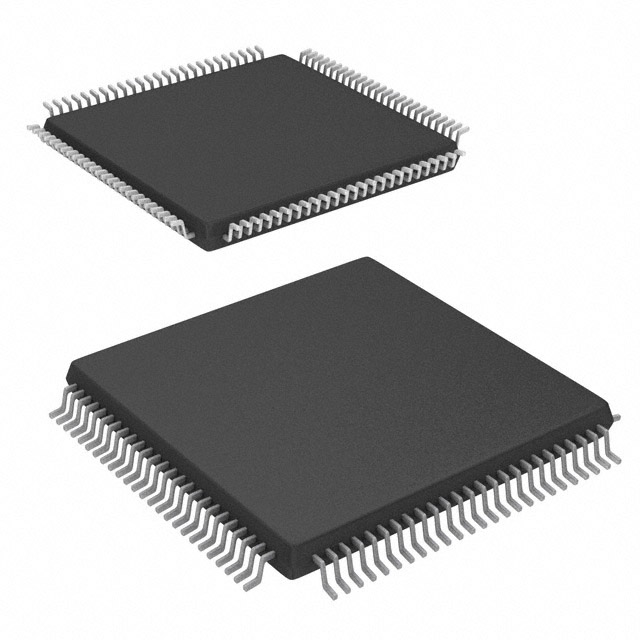

ACEX-1K® Field Programmable Gate Array (FPGA) IC 92 12288 576 144-LQFP |

|---|---|

| Quantity | 982 Available (as of May 5, 2026) |

| Product Category | Field Programmable Gate Array (FPGA) |

|---|---|

| Manufacturer | Intel |

| Manufacturing Status | Obsolete |

| Manufacturer Standard Lead Time | RFQ |

| Datasheet |

Specifications & Environmental

| Device Package | 144-TQFP (20x20) | Grade | Commercial | Operating Temperature | 0°C – 70°C | ||

|---|---|---|---|---|---|---|---|

| Package / Case | 144-LQFP | Number of I/O | 92 | Voltage | 2.375 V - 2.625 V | ||

| Mounting Method | Surface Mount | RoHS Compliance | Unknown | REACH Compliance | REACH Unaffected | ||

| Moisture Sensitivity Level | 3 (168 Hours) | Number of LABs/CLBs | 72 | Number of Logic Elements/Cells | 576 | ||

| Number of Gates | 56000 | ECCN | 3A991D | HTS Code | 8542.39.0001 | ||

| Qualification | N/A | Total RAM Bits | 12288 |

Overview of EP1K10TC144-1N – ACEX-1K® Field Programmable Gate Array (FPGA) IC 92 12288 576 144-LQFP

The EP1K10TC144-1N is an ACEX-1K family programmable logic device providing a compact FPGA solution with embedded memory and general logic fabric. It combines on-chip embedded arrays and logic elements to implement memory-rich megafunctions and general-purpose logic in a single surface-mount 144-LQFP package.

Designed for cost-efficient system-on-a-programmable-chip (SOPC) integration and high-volume applications, the device targets designs that need a balance of logic capacity, embedded RAM, and flexible I/O while operating within commercial temperature and voltage ranges.

Key Features

- Core logic capacity — 576 logic elements and approximately 56,000 equivalent gates provide the programmable logic bed for control, glue-logic, and custom processing functions.

- Embedded memory — Total on-chip RAM of 12,288 bits implemented via embedded array blocks (EABs) suitable for efficient memory and dual-port megafunctions.

- I/O flexibility — Up to 92 user I/O pins with MultiVolt capability on the ACEX-1K family (I/O can drive/receive 2.5-V, 3.3-V, or 5.0-V devices as a family feature noted in the datasheet).

- Package and mounting — 144-LQFP surface-mount package (supplier device package: 144-TQFP, 20 × 20) for compact board-level integration.

- Power and supply — Operates with a specified voltage supply range of 2.375 V to 2.625 V and an internal 2.5-V supply as documented for the ACEX-1K family.

- Commercial operating range — Rated for 0 °C to 70 °C operation (commercial grade).

- System-level features — Family-level features include in-circuit reconfigurability (ICR) via external configuration devices or JTAG, built-in JTAG boundary-scan test (IEEE 1149.1), and programmable I/O options such as open-drain and slew-rate control.

- Interconnect and arithmetic support — Dedicated carry and cascade chains and a continuous routing structure (FastTrack) for predictable interconnect delays and efficient arithmetic implementation.

- Clocking — Low-skew clock distribution trees with support for multiple global clocks and clock-management options noted in the ACEX-1K family.

Typical Applications

- High-performance communications equipment — Implement packet processing, protocol bridging, and custom logic where embedded memory and moderate logic density are required.

- SOPC and megafunction integration — Combine embedded RAM blocks and logic elements to implement memory controllers, FIFOs, and other megafunctions in a single device.

- Embedded control and glue logic — Replace multiple discrete components with a programmable solution for control, timing, and interface adaptation.

- PCI-capable systems (family-level note) — The ACEX-1K family supports PCI Local Bus Specification, Revision 2.2 for 3.3-V operation; family documentation also notes -1 speed-grade devices for 5.0-V operation.

Unique Advantages

- Balanced logic and memory in one device: 576 logic elements combined with 12,288 bits of embedded RAM let you implement both control logic and local buffering without external memory for many use cases.

- Flexible I/O voltage support: Family MultiVolt I/O capability allows interfacing with 2.5-V, 3.3-V, or 5.0-V peripherals, simplifying mixed-voltage board designs.

- In-circuit reconfigurability and testability: ICR via external configuration devices and built-in JTAG boundary-scan support enable field updates and board-level test access without consuming device logic.

- Design predictability: FastTrack interconnect, dedicated carry/cascade chains, and low-skew clock distribution reduce timing uncertainty for arithmetic and high-fan-in functions.

- Compact, surface-mount package: The 144-LQFP (20 × 20) package provides a space-efficient footprint for density- and cost-sensitive PCB layouts.

- Toolchain and ecosystem support: The ACEX-1K family is supported by development systems and interfaces to common EDA tools for design entry, synthesis, and place-and-route.

Why Choose EP1K10TC144-1N?

The EP1K10TC144-1N offers a practical balance of programmable logic, embedded RAM, and flexible I/O in a compact 144-LQFP package, making it well suited to designs that require moderate logic density with on-chip memory and straightforward board-level integration. Its family-level features—such as MultiVolt I/O, in-circuit reconfigurability, and built-in JTAG—support maintainability and field updates while preserving device logic resources.

For teams developing cost-conscious SOPC solutions, communications interfaces, or embedded control systems that operate within commercial temperature and voltage ranges, this device provides a verified platform supported by established development tools and family documentation for design and integration.

Request a quote or submit an RFQ to receive pricing and availability information for the EP1K10TC144-1N.

Date Founded: 1968

Headquarters: Santa Clara, California, USA

Employees: 130,000+

Revenue: $54.23 Billion

Certifications and Memberships: ISO9001:2015, ISO14001:2015, ISO17025:2017, ISO27001:2022, ISO45001:2018, ISO50001:2018