EP1S10F672I7

| Part Description |

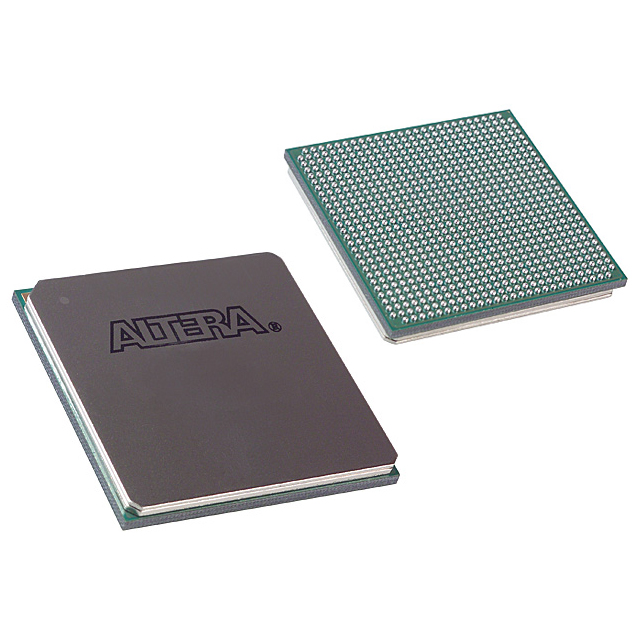

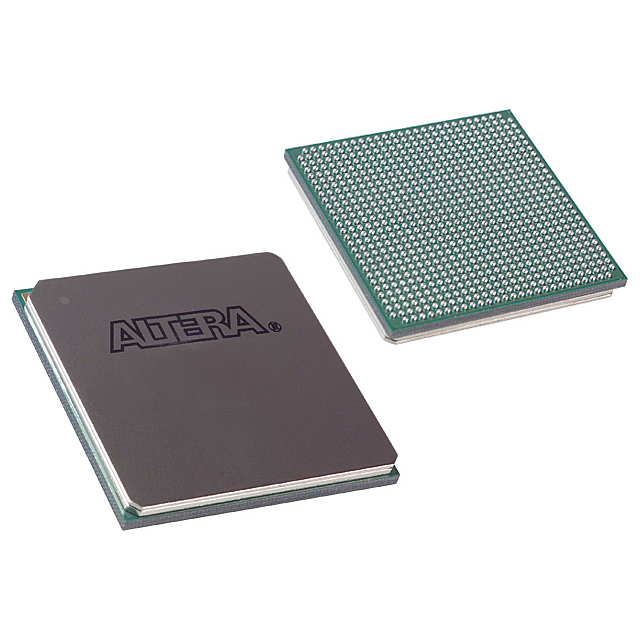

Stratix® Field Programmable Gate Array (FPGA) IC 345 920448 10570 672-BBGA |

|---|---|

| Quantity | 99 Available (as of May 5, 2026) |

| Product Category | Field Programmable Gate Array (FPGA) |

|---|---|

| Manufacturer | Intel |

| Manufacturing Status | Obsolete |

| Manufacturer Standard Lead Time | RFQ |

| Datasheet |

Specifications & Environmental

| Device Package | 672-FBGA (27x27) | Grade | Industrial | Operating Temperature | -40°C – 100°C | ||

|---|---|---|---|---|---|---|---|

| Package / Case | 672-BBGA | Number of I/O | 345 | Voltage | 1.425 V - 1.575 V | ||

| Mounting Method | Surface Mount | RoHS Compliance | RoHS non-compliant | REACH Compliance | REACH Unaffected | ||

| Moisture Sensitivity Level | 3 (168 Hours) | Number of LABs/CLBs | 1057 | Number of Logic Elements/Cells | 10570 | ||

| Number of Gates | N/A | ECCN | 3A991D | HTS Code | 8542.39.0001 | ||

| Qualification | N/A | Total RAM Bits | 920448 |

Overview of EP1S10F672I7 – Stratix® Field Programmable Gate Array (FPGA) IC 345 920448 10570 672-BBGA

The EP1S10F672I7 is a Stratix® field-programmable gate array from Intel, providing a mid-range programmable logic device with integrated memory and a high I/O count. It combines approximately 10,570 logic elements and roughly 0.92 Mbits of on-chip RAM with architecture-level support for clocking, DSP interfaces, and advanced I/O.

Built for industrial-class applications, the device offers a 672‑ball BGA package, a 1.425–1.575 V core supply range, and an operating temperature range of −40 °C to 100 °C, making it suitable for designs that require programmable logic, flexible I/O, and embedded memory within a compact surface-mount package.

Key Features

- Programmable Logic Approximately 10,570 logic elements for implementing control, processing, and glue-logic functions across mid-range designs.

- Embedded Memory Approximately 0.92 Mbits (920,448 bits) of on-chip RAM with support for multiple memory modes and TriMatrix memory architecture as described in the Stratix handbook.

- I/O Capacity & Flexibility 345 user I/O pins supported; device documentation covers advanced I/O structure including double-data-rate interfaces, programmable drive strength, slew-rate control, bus-hold, and multi‑voltage I/O options.

- Clocking & DSP Support Stratix architecture includes PLLs and clock networks, enhanced and fast PLL options, and DSP block interfaces with multiplier and adder/output blocks for arithmetic and timing-critical designs.

- Configuration & Test Features Supports IEEE 1149.1 (JTAG) boundary-scan, SignalTap II embedded logic analyzer, multiple configuration schemes including partial reconfiguration, and device-level monitoring features referenced in the device handbook.

- Package, Power & Thermal Surface-mount 672‑BBGA (documented as 672‑FBGA 27×27); core supply 1.425–1.575 V; industrial operating temperature range −40 °C to 100 °C.

- Compliance RoHS compliant.

Typical Applications

- Industrial Controls Programmable logic and embedded memory enable custom control, motor control interfaces, and system orchestration in industrial automation equipment.

- Data-Path and Signal Processing On-chip RAM and DSP block interfaces support buffering and arithmetic functions for mid-range signal-processing tasks and protocol handling.

- High‑Density I/O Systems 345 I/O pins and advanced I/O features make the device suitable for instrumentation, test equipment, and I/O-rich communication interfaces.

- Configurable Prototyping Programmability, JTAG boundary-scan, and embedded logic-analysis capability support in-system debug and iterative design validation.

Unique Advantages

- Mid‑Range Integration: Approximately 10,570 logic elements and substantial embedded RAM reduce external component count for many applications.

- High I/O Density: 345 I/O pins provide abundant external connectivity for multi-channel interfaces and complex board-level routing.

- Flexible Clocking and DSP Support: Integrated PLLs, clock networks, and DSP block interfaces enable advanced timing architectures and arithmetic processing without adding external timing ICs.

- Industrial Temperature Range: Rated for −40 °C to 100 °C operation, supporting deployment in temperature-variable environments.

- Compact, Surface‑Mount Packaging: 672‑BBGA (27×27 FBGA) balances high pin count and a compact footprint for space-constrained designs.

- Standards and Testability: JTAG boundary-scan and embedded logic-analysis support simplify manufacturing test and in-system debug workflows.

Why Choose EP1S10F672I7?

The EP1S10F672I7 positions itself as a solid choice for designers needing a Stratix-class FPGA with a balanced mix of logic resources, embedded memory, and extensive I/O—all in an industrial-temperature, RoHS-compliant package. Its architecture-level support for clocking, DSP interfacing, and configuration/test features makes it suitable for applications that require programmable flexibility combined with reliable thermal and electrical operating ranges.

This device is well suited for engineering teams building industrial control systems, I/O-dense instrumentation, or mid-range signal-processing platforms that benefit from on-chip RAM, a high I/O count, and the configuration and test capabilities described in the Stratix device handbook.

Request a quote or submit an inquiry to receive pricing and availability information for EP1S10F672I7.

Date Founded: 1968

Headquarters: Santa Clara, California, USA

Employees: 130,000+

Revenue: $54.23 Billion

Certifications and Memberships: ISO9001:2015, ISO14001:2015, ISO17025:2017, ISO27001:2022, ISO45001:2018, ISO50001:2018