MT28F128J3RP-12 MET TR

| Part Description |

IC FLASH 128MBIT PARALLEL 56TSOP |

|---|---|

| Quantity | 579 Available (as of May 5, 2026) |

| Product Category | Memory |

|---|---|

| Manufacturer | Micron Technology Inc. |

| Manufacturing Status | Obsolete |

| Manufacturer Standard Lead Time | RFQ |

| Datasheet |

Specifications & Environmental

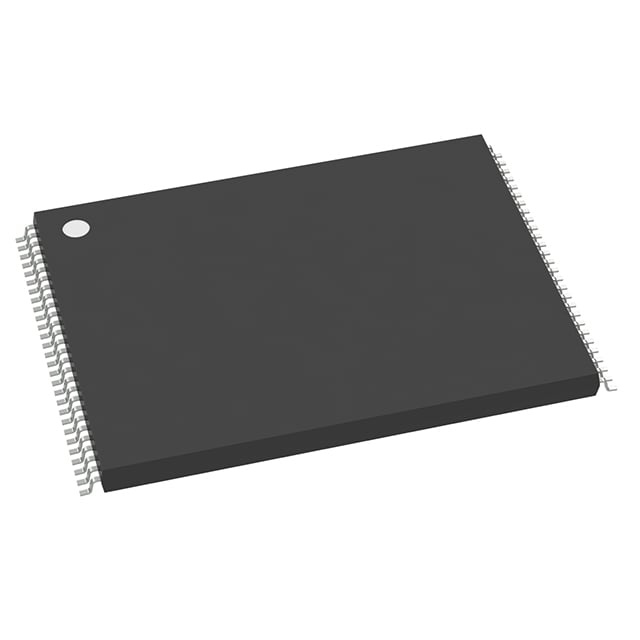

| Device Package | 56-TSOP | Memory Format | FLASH | Technology | FLASH | ||

|---|---|---|---|---|---|---|---|

| Memory Size | 128 Mbit | Access Time | 120 ns | Grade | Industrial | ||

| Clock Frequency | N/A | Voltage | 2.7V ~ 3.6V | Memory Type | Non-Volatile | ||

| Operating Temperature | -40°C ~ 85°C (TA) | Write Cycle Time Word Page | N/A | Packaging | 56-TFSOP (0.724", 18.40mm Width) | ||

| Mounting Method | Non-Volatile | Memory Interface | Parallel | Memory Organization | 16M x 8, 8M x 16 | ||

| Moisture Sensitivity Level | 4 (72 Hours) | RoHS Compliance | ROHS3 Compliant | REACH Compliance | REACH Unaffected | ||

| Qualification | N/A | ECCN | 3A991B1A | HTS Code | 8542.32.0071 |

Overview of MT28F128J3RP-12 MET TR – IC FLASH 128MBIT PARALLEL 56TSOP

The MT28F128J3RP-12 MET TR is a 128 Mbit non-volatile FLASH memory device offered in a 56-pin TSOP Type I package. It provides parallel interface access with memory organizations of 16M × 8 or 8M × 16 and supports VCC operation from 2.7 V to 3.6 V.

Designed for systems requiring on-board code or data storage, the device combines asynchronous page-mode read performance (120 ns read access time for the 128 Mb device) with built-in write/erase algorithms, protection registers, and suspend features to support robust firmware and data management.

Key Features

- Memory Core The device is a 128 Mbit Q‑FLASH® memory organized as 16M × 8 or 8M × 16 with one hundred twenty-eight 128 KB erase blocks.

- Read Performance Asynchronous page-mode reads with a 120 ns read access time (128 Mb); includes 25 ns internal page-mode timing in datasheet timing options.

- Power and Programming VCC, VCCQ, and VPEN operate from 2.7 V to 3.6 V; supports 2.7 V to 3.6 V application programming.

- Package & Temperature Supplied in a 56‑pin TSOP Type I (56‑TFSOP, 18.40 mm width) with an operating temperature range of −40 °C to +85 °C (TA).

- Interface Parallel memory interface with industry-standard pinout and fully TTL‑compatible inputs and outputs.

- Data Protection & Security 128‑bit protection register, 64‑bit unique device identifier, 64‑bit user‑programmable OTP cells, and enhanced protection features (VPEN = VSS) including flexible sector locking and lockout during power transitions.

- Reliability & Endurance Automatic write and erase algorithms, 5.6 μs per‑byte effective programming using the write buffer, automatic suspend options, and specified endurance of 100,000 erase cycles per block.

- Standards & Compatibility Common Flash Interface (CFI) and Scalable Command Set support; manufacturer identification codes for Micron (0x2C) and Intel (0x89).

Typical Applications

- Embedded firmware storage Non-volatile 128 Mbit FLASH with parallel interface and on‑chip protection features for storing system firmware and boot code.

- Code and data storage in industrial systems Extended temperature range (−40 °C to +85 °C) and robust erase/program endurance suit embedded controllers and industrial electronics.

- System configuration and identification 64‑bit unique device identifier and user‑programmable OTP cells enable device-specific configuration and secure identifiers.

Unique Advantages

- Flexible memory organization: Two organization options (16M × 8, 8M × 16) let designers match bus width and capacity requirements without changing core device characteristics.

- Parallel interface simplicity: Industry‑standard parallel pinout and TTL‑compatible I/O simplify integration into existing parallel bus systems.

- Wide supply and programming range: 2.7 V to 3.6 V operation and programming reduces power-supply complexity across varied system designs.

- Block-level protection and security: 128‑bit protection register plus OTP and unique ID options support secure storage and flexible sector locking strategies.

- Suspend and resume control: Automatic suspend options for erase and program operations enable read or program suspend-to-read behavior, improving system responsiveness during background operations.

- Proven endurance: Specified 100,000 erase cycles per block supports repeated program/erase cycles over product lifetime.

Why Choose MT28F128J3RP-12 MET TR?

The MT28F128J3RP-12 MET TR positions itself as a robust, parallel‑interface FLASH memory option for embedded systems requiring 128 Mbit of non‑volatile storage. Its combination of flexible memory organization, on‑chip protection and identification features, and suspendable erase/program operations makes it suitable for designs that need reliable firmware and data storage with predictable endurance.

This device is well suited for engineers and procurement teams designing systems that require a TSOP‑packaged parallel FLASH with extended temperature support, defined read performance (120 ns for 128 Mb), and comprehensive protection and programming features documented in the product datasheet.

Request a quote or submit a procurement inquiry to receive pricing, availability, and lead‑time details for the MT28F128J3RP-12 MET TR.