MT40A4G8NEA-062E:F TR

| Part Description |

IC DRAM 32GBIT PARALLEL 78FBGA |

|---|---|

| Quantity | 1,564 Available (as of May 5, 2026) |

| Product Category | Memory |

|---|---|

| Manufacturer | Micron Technology Inc. |

| Manufacturing Status | Obsolete |

| Manufacturer Standard Lead Time | RFQ |

| Datasheet |

Specifications & Environmental

| Device Package | 78-FBGA (7.5x11) | Memory Format | DRAM | Technology | SDRAM - DDR4 | ||

|---|---|---|---|---|---|---|---|

| Memory Size | 32 Gbit | Access Time | 13.75 ns | Grade | Extended / Automotive-like | ||

| Clock Frequency | 1.6 GHz | Voltage | 1.14V ~ 1.26V | Memory Type | Volatile | ||

| Operating Temperature | 0°C ~ 95°C (TC) | Write Cycle Time Word Page | N/A | Packaging | 78-TFBGA | ||

| Mounting Method | Volatile | Memory Interface | Parallel | Memory Organization | 4G x 8 | ||

| Moisture Sensitivity Level | 3 (168 Hours) | RoHS Compliance | ROHS Compliant | REACH Compliance | REACH Unaffected | ||

| Qualification | N/A | ECCN | N/A | HTS Code | N/A |

Overview of MT40A4G8NEA-062E:F TR – IC DRAM 32GBIT PARALLEL 78FBGA

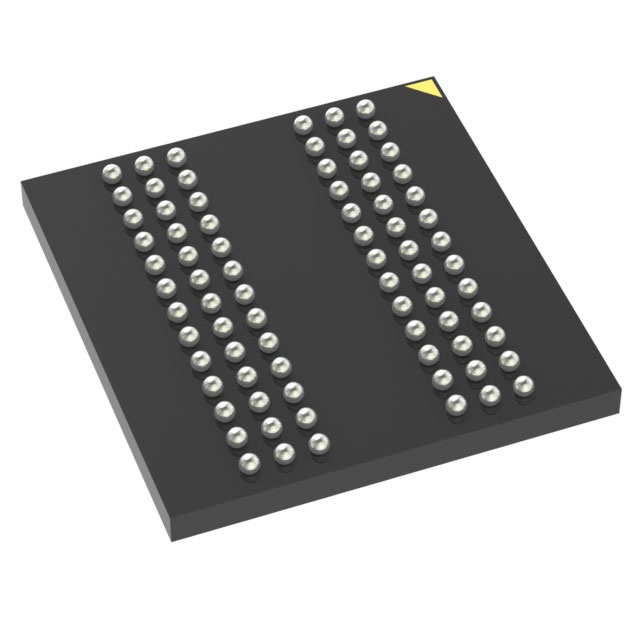

The MT40A4G8NEA-062E:F TR is a 32 Gbit TwinDie™ DDR4 SDRAM organized as 4G x 8 with a parallel memory interface. It combines two 16Gb DDR4 die in a dual‑rank configuration to deliver high density DDR4 memory in a 78-ball TFBGA package.

Designed for systems that require high-density, dual‑rank DDR4 memory, this device provides JEDEC‑standard ballout, 1.2 V class operation (1.14–1.26 V), and a commercial operating temperature range up to 95°C for board‑level integration where a compact FBGA package and high data rate are required.

Key Features

- Architecture TwinDie™ implementation using two 16Gb Micron DDR4 die to form a 32Gb device with two ranks (dual CS#, ODT, and CKE balls).

- Memory Organization 128M x 8 organization (4G x 8) with 16 banks per die and bank grouping to support concurrent bank operation.

- DDR4 Performance Speed grade -062E supports DDR4-3200 data rate with target timing of CL‑22 and key timing parameters (tAA, tRCD, tRP) at 13.75 ns.

- Interface Parallel DDR4 SDRAM interface with VDDQ‑terminated I/O at 1.2 V nominal.

- Voltage VDD = VDDQ = 1.2 V operation with specified supply range of 1.14 V to 1.26 V.

- Package 78‑ball TFBGA (78‑FBGA NEA: 7.5 mm × 11 mm × 1.2 mm) low‑profile package for board‑level mounting.

- Temperature & Refresh Commercial temperature range TC = 0°C to 95°C; 8192 refresh cycles in 64 ms (0–85°C) and 8192 refresh cycles in 32 ms (85–95°C).

- Timing Clock frequency listed as 1.6 GHz (DDR data rate 3200 MT/s), with access times specified at 13.75 ns for key cycles.

Typical Applications

- High‑density DDR4 memory subsystems For designs requiring a 32 Gbit parallel DDR4 device in a dual‑rank configuration for increased memory density.

- Board‑level memory modules Integration into compact FBGA board designs where a low‑profile 78‑ball package is required.

- High‑data‑rate interfaces Systems targeting DDR4‑3200 performance with CL‑22 timing and 1.2 V I/O termination.

Unique Advantages

- Dual‑rank TwinDie™ construction: Provides two ranks in a single 32Gb package using Micron 16Gb die, enabling higher memory density without additional components.

- JEDEC‑standard ballout and low‑profile FBGA: Simplifies board implementation with a standard 78‑ball TFBGA footprint (7.5 mm × 11 mm × 1.2 mm).

- High data rate with defined timing: Supports DDR4‑3200 (speed grade -062E) with CL‑22 and 13.75 ns key timing parameters for predictable performance.

- 1.2 V nominal operation: VDD and VDDQ operation in the 1.14–1.26 V range with VDDQ‑terminated I/O for standard DDR4 signaling.

- Commercial temperature range to 95°C: Operable from 0°C to 95°C with specified refresh requirements for elevated temperature operation.

Why Choose MT40A4G8NEA-062E:F TR?

The MT40A4G8NEA-062E:F TR positions itself as a compact, high‑density DDR4 memory device that delivers two ranks of Micron 16Gb DDR4 die in a single 78‑ball FBGA package. Its DDR4‑3200 speed grade, defined CL‑22 timing, and 1.2 V class operation make it suitable for designs that need predictable DDR4 performance and a low‑profile board footprint.

This device is appropriate for engineers and designers building memory subsystems or board‑level solutions that require increased memory capacity, JEDEC‑standard ballout, and operation across a commercial temperature range. The TwinDie approach provides density and rank flexibility while maintaining standard DDR4 electrical and timing characteristics.

Request a quote or submit a pricing inquiry to receive availability, lead‑time, and ordering information for MT40A4G8NEA-062E:F TR.