IS42S16800E-75EBL

| Part Description |

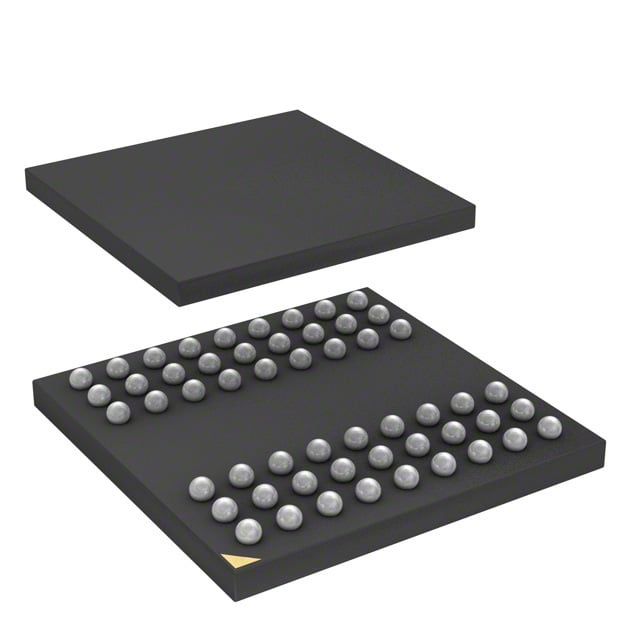

IC DRAM 128MBIT PAR 54TFBGA |

|---|---|

| Quantity | 49 Available (as of May 5, 2026) |

| Product Category | Memory |

|---|---|

| Manufacturer | Integrated Silicon Solution Inc |

| Manufacturing Status | Obsolete |

| Manufacturer Standard Lead Time | RFQ |

| Datasheet |

Specifications & Environmental

| Device Package | 54-TFBGA (8x8) | Memory Format | DRAM | Technology | SDRAM | ||

|---|---|---|---|---|---|---|---|

| Memory Size | 128 Mbit | Access Time | 5.4 ns | Grade | Commercial | ||

| Clock Frequency | 133 MHz | Voltage | 3V ~ 3.6V | Memory Type | Volatile | ||

| Operating Temperature | 0°C ~ 70°C (TA) | Write Cycle Time Word Page | N/A | Packaging | 54-TFBGA | ||

| Mounting Method | Volatile | Memory Interface | Parallel | Memory Organization | 8M x 16 | ||

| Moisture Sensitivity Level | 3 (168 Hours) | RoHS Compliance | ROHS3 Compliant | REACH Compliance | REACH Unaffected | ||

| Qualification | N/A | ECCN | EAR99 | HTS Code | 8542.32.0002 |

Overview of IS42S16800E-75EBL – 128Mbit SDRAM, 54-TFBGA

The IS42S16800E-75EBL is a 128 Mbit synchronous DRAM (SDRAM) device from Integrated Silicon Solution Inc (ISSI), organized as 8M × 16 with a parallel memory interface. It implements a fully synchronous, pipeline architecture with a quad-bank organization and LVTTL signaling for high-speed, clocked memory operations.

This device targets systems requiring compact, parallel SDRAM in a 54-ball TF‑BGA (8×8) package and supports features such as programmable burst length and sequence, auto- and self-refresh, and operation at 3.0–3.6 V with an ambient temperature range of 0°C to 70°C.

Key Features

- Core Architecture Fully synchronous pipeline SDRAM with internal quad-bank organization (4 banks) and all inputs/outputs referenced to the rising edge of CLK.

- Memory Organization 128 Mbit total capacity configured as 8M × 16, delivering 33,554,432-bit banks suitable for parallel memory systems.

- Performance Supported clock frequencies include up to 133 MHz for the -75E grade; access time from clock can be 5.4 ns (CAS latency = 2 for the -75E grade).

- Programmable Burst & Timing Programmable burst lengths (1, 2, 4, 8, full page) and burst sequence options (sequential or interleave); selectable CAS latency (2 or 3 clocks) where applicable.

- Refresh & Power Modes Auto Refresh and Self Refresh supported with 4096 refresh cycles every 64 ms; includes power-down capability.

- Interface & Signaling Parallel memory interface with LVTTL-compatible signals for command and control.

- Power Supply VDD and VDDQ nominal 3.3 V operation; device supply range listed as 3.0 V to 3.6 V.

- Package 54-ball TF‑BGA (8×8) compact package (54-TFBGA) for space-constrained board designs.

- Operating Conditions Specified ambient operating temperature range of 0°C to 70°C (TA).

Typical Applications

- Parallel SDRAM memory expansion Integration into systems that require a 128 Mbit parallel SDRAM device with LVTTL signaling and compact BGA packaging.

- High-speed buffering and burst access Use where programmable burst lengths, burst sequencing and fast clock-referenced access are needed for burst read/write operations.

- Systems requiring refresh management Designs that rely on automatic and self-refresh modes (4096 refresh cycles per 64 ms) to maintain data integrity.

Unique Advantages

- Clocked, synchronous pipeline architecture: All signals referenced to the rising clock edge provide deterministic timing for tight memory control.

- Flexible burst control: Programmable burst lengths and sequence modes enable matching memory transfers to system access patterns.

- Compact BGA footprint: 54-TFBGA (8×8) package offers a small board area for space-constrained designs while maintaining parallel interface connectivity.

- Robust refresh capabilities: Auto Refresh and Self Refresh support with specified refresh cycle requirements simplifies system refresh handling.

- Wide supply tolerance: Operation across 3.0 V to 3.6 V supplies enables compatibility with typical 3.3 V memory power rails.

Why Choose IS42S16800E-75EBL?

The IS42S16800E-75EBL delivers a compact, synchronous 128 Mbit DRAM solution built around a pipeline, quad-bank architecture that supports programmable burst operation and clock-referenced timing. Its 54-ball TF‑BGA package and LVTTL interface make it suitable for designs that require a parallel SDRAM with controlled timing and refresh capabilities.

This device is appropriate for designs that need deterministic, clocked memory behavior with flexible burst options and integrated refresh modes, offering predictable access timing (e.g., 5.4 ns access from clock for the -75E grade) and standard 3.3 V class supply operation.

Request a quote or submit a quote request for the IS42S16800E-75EBL to obtain availability and pricing information for your design requirements.