IS43DR16320C-25DBI-TR

| Part Description |

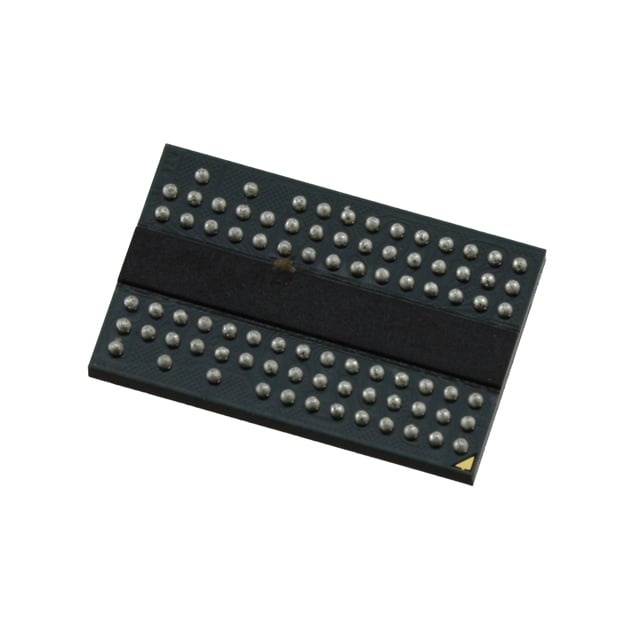

IC DRAM 512MBIT PAR 84TWBGA |

|---|---|

| Quantity | 961 Available (as of May 5, 2026) |

| Product Category | Memory |

|---|---|

| Manufacturer | Integrated Silicon Solution Inc |

| Manufacturing Status | Obsolete |

| Manufacturer Standard Lead Time | RFQ |

| Datasheet |

Specifications & Environmental

| Device Package | 84-TWBGA (8x12.5) | Memory Format | DRAM | Technology | SDRAM - DDR2 | ||

|---|---|---|---|---|---|---|---|

| Memory Size | 512 Mbit | Access Time | 400 ps | Grade | Industrial | ||

| Clock Frequency | 400 MHz | Voltage | 1.7V ~ 1.9V | Memory Type | Volatile | ||

| Operating Temperature | -40°C ~ 85°C (TA) | Write Cycle Time Word Page | 15 ns | Packaging | 84-TFBGA | ||

| Mounting Method | Volatile | Memory Interface | Parallel | Memory Organization | 32M x 16 | ||

| Moisture Sensitivity Level | 3 (168 Hours) | RoHS Compliance | ROHS Compliant | REACH Compliance | REACH Unaffected | ||

| Qualification | N/A | ECCN | EAR99 | HTS Code | 8542.32.0028 |

Overview of IS43DR16320C-25DBI-TR – IC DRAM 512MBIT PAR 84TWBGA

The IS43DR16320C-25DBI-TR is a 512 Mbit DDR2 SDRAM organized as 32M × 16 with a parallel memory interface in a compact 84‑ball WBGA package. It implements a double-data-rate architecture with a 4‑n prefetch to deliver high-speed data transfers and deterministic timing for memory subsystems.

Designed for space-constrained boards requiring high-speed DDR2 memory, the device offers programmable latency, on-die termination and adjustable output drive strength to aid signal integrity and timing optimization across a range of system designs.

Key Features

- Memory Core 512 Mbit DDR2 SDRAM organized as 32M × 16 with 4 internal banks and 4‑bit prefetch architecture.

- Double-Data-Rate Interface Two data transfers per clock cycle with differential data strobe (DQS / ĎQS) and on-chip DLL to align DQ and DQS with CK.

- Programmable Timing Supports programmable CAS latency (CL = 3, 4, 5, 6) and programmable additive latency (AL = 0–5), plus posted CAS; programmable burst lengths of 4 or 8.

- Signal Integrity & Drive On-die termination (ODT) and adjustable data-output drive strength provide options to tune signal integrity for different board layouts.

- Performance Clock frequency listed at 400 MHz with an access time of 400 ps and write cycle time (word page) of 15 ns.

- Power Supply range 1.7 V to 1.9 V (VDD/VDDQ nominal 1.8 V ±0.1 V as specified in the device documentation).

- Package and Size 84‑ball WBGA package (8 mm × 12.5 mm) providing a compact footprint for high-density applications.

- Operating Temperature Specified ambient operating range −40 °C to 85 °C (TA).

Typical Applications

- Embedded systems — Provides high-density DDR2 storage in compact, board-level memory subsystems where space and timing control are important.

- Industrial equipment — Suitable for systems operating across the specified −40 °C to 85 °C ambient range that require deterministic DDR2 memory timing.

- Compact consumer electronics — Fits small form-factor designs needing a 512 Mbit DDR2 memory in an 84‑ball WBGA package.

Unique Advantages

- Double-data-rate throughput: The DDR2 architecture and differential DQS enable two transfers per clock cycle for efficient high-speed data movement.

- Flexible timing control: Programmable CAS and additive latency options plus posted CAS allow designers to tune performance to system timing requirements.

- Signal integrity options: On-die termination and adjustable drive strengths help manage reflections and drive characteristics without external components.

- Compact, high-density package: The 84‑ball WBGA (8 mm × 12.5 mm) keeps board footprint small while delivering 512 Mbit density.

- Industrial temperature capability: Specified for −40 °C to 85 °C ambient operation for deployment in temperature-variant environments.

Why Choose IS43DR16320C-25DBI-TR?

The IS43DR16320C-25DBI-TR positions itself as a compact, configurable DDR2 memory device that balances density, speed and board-level integration. Its programmable latency, ODT and drive strength adjustments give system designers precise control over timing and signal integrity in tight footprint applications.

This device is well suited to designs that require a 512 Mbit parallel DDR2 solution in an 84‑ball WBGA package with a defined supply range (1.7 V–1.9 V) and an ambient operating range down to −40 °C. The combination of DDR2 double-data-rate architecture and on-chip timing features supports scalable performance and predictable behavior across a variety of board implementations.

If you need pricing or availability, request a quote or contact sales to submit a quote for the IS43DR16320C-25DBI-TR.