MT28F128J3BS-12 ET

| Part Description |

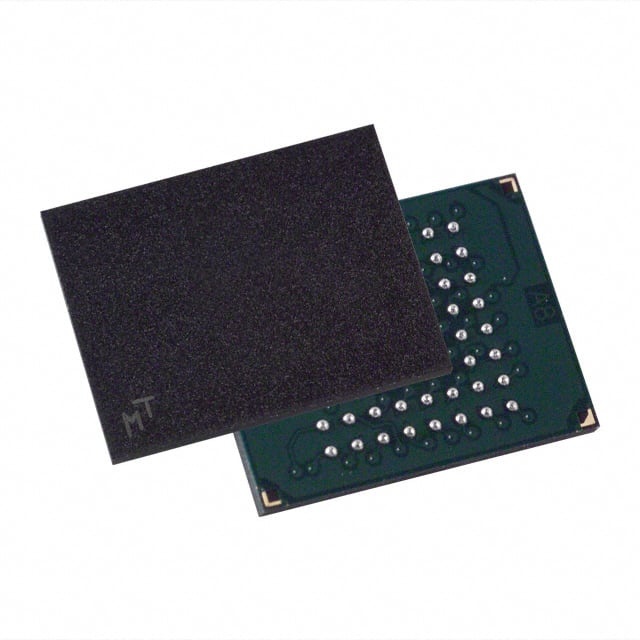

IC FLASH 128MBIT PARALLEL 64FBGA |

|---|---|

| Quantity | 1,398 Available (as of May 5, 2026) |

| Product Category | Memory |

|---|---|

| Manufacturer | Micron Technology Inc. |

| Manufacturing Status | Obsolete |

| Manufacturer Standard Lead Time | RFQ |

| Datasheet |

Specifications & Environmental

| Device Package | 64-FBGA (10x13) | Memory Format | FLASH | Technology | FLASH | ||

|---|---|---|---|---|---|---|---|

| Memory Size | 128 Mbit | Access Time | 120 ns | Grade | Industrial | ||

| Clock Frequency | N/A | Voltage | 2.7V ~ 3.6V | Memory Type | Non-Volatile | ||

| Operating Temperature | -40°C ~ 85°C (TA) | Write Cycle Time Word Page | N/A | Packaging | 64-FBGA | ||

| Mounting Method | Non-Volatile | Memory Interface | Parallel | Memory Organization | 16M x 8, 8M x 16 | ||

| Moisture Sensitivity Level | 4 (72 Hours) | RoHS Compliance | ROHS Compliant | REACH Compliance | REACH Unaffected | ||

| Qualification | N/A | ECCN | 3A991B1A | HTS Code | 8542.32.0071 |

Overview of MT28F128J3BS-12 ET – IC FLASH 128Mbit Parallel 64-FBGA

The MT28F128J3BS-12 ET is a 128 Mbit non-volatile FLASH memory device in a 64-ball FBGA (10×13) package with a parallel interface. It implements Micron’s Q-FLASH architecture with x8/x16 organization and industry-standard pinout for TTL-compatible inputs and outputs.

This device is designed for systems that require parallel FLASH storage with defined timing and power envelopes: 120 ns read access (128 Mb), 2.7 V–3.6 V supply operation, and an extended operating temperature range of −40°C to +85°C.

Key Features

- Memory Capacity & Organization — 128 Mbit total capacity organized as 16M × 8 or 8M × 16, providing flexible bus-width options for system integration.

- Architecture & Erase Granularity — Q-FLASH device with one hundred twenty 128 KB erase blocks (for the 128 Mb density), enabling block-based erase and management.

- Read Performance — Asynchronous page mode reads with 120 ns primary read access time (128 Mb) and 25 ns secondary timing metric.

- Power & Programming — Operates and programs at VCC/VCCQ/VPEN from 2.7 V to 3.6 V; effective programming via write buffer yields 5.6 μs-per-byte effective programming time using the write-buffer algorithm.

- Data Protection & Security — 128-bit protection register, 64-bit unique device identifier, 64-bit user-programmable OTP cells, enhanced data protection feature with VPEN = VSS, and flexible sector locking with lockout during power transitions.

- Reliability & Lifecycle — Specified for 100,000 erase cycles per block and supports automatic suspend options (block erase/program suspend-to-read and program suspend-to-read) to improve system responsiveness during maintenance operations.

- Interface & Compatibility — Parallel memory interface with industry-standard pinout; inputs and outputs are fully TTL-compatible. Includes Common Flash Interface (CFI) and Scalable Command Set support.

- Package & Temperature — 64-FBGA (10×13) supplier device package with an extended operating temperature range of −40°C to +85°C (TA).

Typical Applications

- Firmware and Code Storage — Non-volatile FLASH storage for system firmware and boot code in embedded platforms requiring parallel memory access.

- System Configuration Storage — Storage of configuration tables, device identifiers, and user-programmable OTP data where block-level erase and protection are required.

- Industrial and Extended-Temperature Systems — Use in systems operating across −40°C to +85°C that need robust erase/program endurance and protection features.

Unique Advantages

- Flexible Bus Widths — Support for x8 and x16 organizations enables adaptation to multiple system bus architectures without changing core device features.

- Block-Level Control — 128 KB erase block architecture and sector locking provide fine-grained control for firmware updates and data protection.

- Extended Voltage Range — 2.7 V–3.6 V operation simplifies integration with common 3.3 V system rails.

- Integrated Identification & Security — 64-bit unique device identifier and 64-bit user-programmable OTP cells allow device-level tracking and secure storage of critical data.

- Suspend/Resume Operations — Automatic suspend options (erase/program suspend-to-read) allow reads to continue during long program/erase cycles, improving system availability.

- Defined Endurance & Programming Metrics — 100,000 erase cycles per block and 5.6 μs-per-byte effective programming time using the write buffer provide verifiable lifecycle and performance characteristics.

Why Choose MT28F128J3BS-12 ET?

The MT28F128J3BS-12 ET positions itself as a robust parallel FLASH option when designers need a 128 Mbit non-volatile memory with clear electrical and timing specifications. Its combination of x8/x16 organization, block-based erase architecture, extended temperature range, and industry-standard pinout simplifies integration into existing parallel-memory systems.

This device is suited for designs that require defined endurance, device identification, programmable OTP cells, and sector protection features. The VCC/VCCQ/VPEN voltage range and FBGA packaging provide a compact, reliable component choice for embedded and industrial applications where parallel FLASH is required.

To request a quote or discuss availability and lead times for the MT28F128J3BS-12 ET, please submit a quote request or contact sales for further assistance.