MT46V32M16BN-5B:F TR

| Part Description |

IC DRAM 512MBIT PARALLEL 60FBGA |

|---|---|

| Quantity | 840 Available (as of May 5, 2026) |

| Product Category | Memory |

|---|---|

| Manufacturer | Micron Technology Inc. |

| Manufacturing Status | Obsolete |

| Manufacturer Standard Lead Time | RFQ |

| Datasheet |

Specifications & Environmental

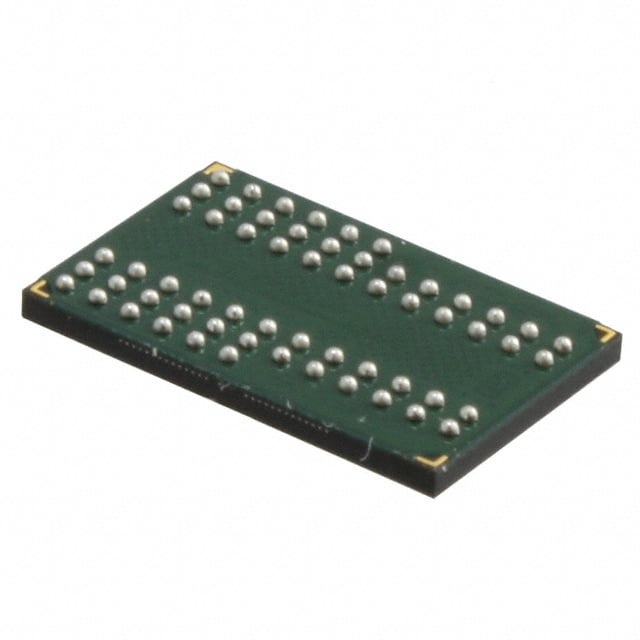

| Device Package | 60-FBGA (10x12.5) | Memory Format | DRAM | Technology | SDRAM - DDR | ||

|---|---|---|---|---|---|---|---|

| Memory Size | 512 Mbit | Access Time | 700 ps | Grade | Commercial | ||

| Clock Frequency | 200 MHz | Voltage | 2.5V ~ 2.7V | Memory Type | Volatile | ||

| Operating Temperature | 0°C ~ 70°C (TA) | Write Cycle Time Word Page | 15 ns | Packaging | 60-TFBGA | ||

| Mounting Method | Volatile | Memory Interface | Parallel | Memory Organization | 32M x 16 | ||

| Moisture Sensitivity Level | 3 (168 Hours) | RoHS Compliance | ROHS3 Compliant | REACH Compliance | REACH Unaffected | ||

| Qualification | N/A | ECCN | EAR99 | HTS Code | 8542.32.0024 |

Overview of MT46V32M16BN-5B:F TR – IC DRAM 512Mbit Parallel 60FBGA

The MT46V32M16BN-5B:F TR is a 512 Mbit DDR SDRAM device organized as 32M × 16 with four internal banks and a parallel memory interface. It implements double-data-rate (DDR) architecture with source-synchronous DQS signaling and a DLL for timing alignment.

Designed for commercial-temperature applications, the device targets systems that require 512 Mbit of volatile DDR memory operating from a 2.5V supply range and supporting up to 200 MHz clocking in a compact 60-ball FBGA (10 mm × 12.5 mm) package.

Key Features

- Core DDR Architecture Internal pipelined double-data-rate (DDR) design delivering two data accesses per clock cycle with differential clock inputs (CK, CK#) and command capture on the positive CK edge.

- Memory Organization 512 Mbit capacity organized as 32M × 16 with four internal banks for concurrent operation and a parallel DQ interface.

- Data Strobe and Masking Bidirectional data strobe (DQS) is transmitted/received with data (x16 devices have two DQS lines, one per byte); Data Mask (DM) provided for write-data masking (x16 has two).

- Timing and Performance Supports a clock frequency up to 200 MHz (speed grade -5B) with access-time specification of approximately 700 ps and a write cycle time (word page) of 15 ns.

- Voltage and I/O VDD/VDDQ operation in the 2.5 V ± tolerances (product data lists 2.5 V ~ 2.7 V supply range); I/O uses 2.5 V signaling.

- Refresh and Power Management Auto-refresh supported with 8K refresh cycles (64 ms for commercial devices) and optional self-refresh modes described in the device documentation.

- Programmable Burst and Control Programmable burst lengths of 2, 4, or 8 and support for concurrent auto-precharge and tRAS lockout mechanisms.

- Package and Temperature Supplied in a 60-ball FBGA package (10 mm × 12.5 mm); commercial operating temperature rated from 0 °C to +70 °C.

Typical Applications

- 2.5 V DDR memory subsystems — Provides 512 Mbit of DDR SDRAM capacity in designs that require a parallel DDR interface and source-synchronous DQS timing.

- Compact board-level implementations — Small 60-ball FBGA (10 mm × 12.5 mm) package for space-constrained PCBs needing DDR memory.

- Commercial-temperature electronic equipment — Suited for systems operating within 0 °C to +70 °C that require DDR400 timing capability at the specified speed grade.

Unique Advantages

- Double-data-rate throughput: Two data transfers per clock cycle improve effective bandwidth relative to single-rate DRAM while using the same clocking domain.

- Byte-granular strobes and masking: Separate DQS and DM per byte (x16 configuration provides two of each) enable accurate timing capture and selective write masking.

- Timing alignment via DLL: On-die DLL aligns DQ/DQS transitions with CK for improved data eye alignment and reliable source-synchronous operation.

- Flexible burst control: Programmable burst lengths (2, 4, 8) allow tuning of transfer granularity to match system transaction patterns.

- Compact FBGA packaging: 60-ball FBGA (10 mm × 12.5 mm) reduces board footprint while providing the required I/O count for x16 DDR configurations.

- Commercial-grade temperature support: Rated for 0 °C to +70 °C operation, matching common commercial electronic product requirements.

Why Choose MT46V32M16BN-5B:F TR?

The MT46V32M16BN-5B:F TR delivers a 512 Mbit DDR SDRAM solution with a 32M × 16 organization, source-synchronous DQS, DLL timing alignment, and support for up to 200 MHz operation at the specified speed grade. Its 60-ball FBGA package and 2.5 V I/O make it suitable for compact commercial designs that require parallel DDR memory with programmable burst lengths and standard refresh management.

This device is appropriate for engineers specifying a verified DDR memory component with documented timing, voltage, and thermal ranges. Detailed device characteristics and timing tables are provided in the Micron product documentation to support system integration and timing closure.

Request a quote or submit an inquiry for pricing and availability of the MT46V32M16BN-5B:F TR.