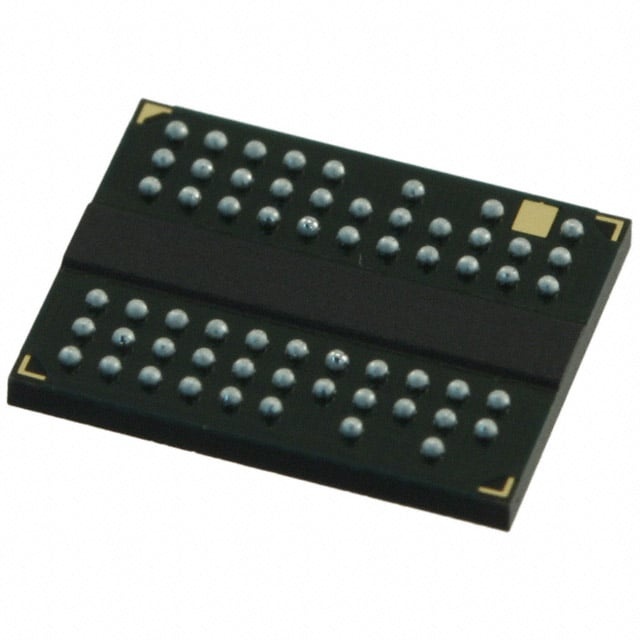

MT47H128M4CB-37E:B

| Part Description |

IC DRAM 512MBIT PAR 60FBGA |

|---|---|

| Quantity | 274 Available (as of May 6, 2026) |

| Product Category | Memory |

|---|---|

| Manufacturer | Micron Technology Inc. |

| Manufacturing Status | Obsolete |

| Manufacturer Standard Lead Time | RFQ |

| Datasheet |

Specifications & Environmental

| Device Package | 60-FBGA | Memory Format | DRAM | Technology | SDRAM - DDR2 | ||

|---|---|---|---|---|---|---|---|

| Memory Size | 512 Mbit | Access Time | 500 ps | Grade | Commercial (Extended) | ||

| Clock Frequency | 267 MHz | Voltage | 1.7V ~ 1.9V | Memory Type | Volatile | ||

| Operating Temperature | 0°C ~ 85°C (TC) | Write Cycle Time Word Page | 15 ns | Packaging | 60-FBGA | ||

| Mounting Method | Volatile | Memory Interface | Parallel | Memory Organization | 128M x 4 | ||

| Moisture Sensitivity Level | 5 (48 Hours) | RoHS Compliance | ROHS3 Compliant | REACH Compliance | REACH Unaffected | ||

| Qualification | N/A | ECCN | EAR99 | HTS Code | 8542.32.0024 |

Overview of MT47H128M4CB-37E:B – 512 Mbit DDR2 SDRAM, 60-FBGA

The MT47H128M4CB-37E:B is a 512 Mbit DDR2 SDRAM organized as 128M × 4 with a parallel memory interface in a 60-ball FBGA package. It implements DDR2 architecture with a 4n-bit prefetch, programmable CAS latency and features such as on-die termination and a DLL for DQ/DQS alignment.

Designed for commercial-temperature systems, this device operates from 0°C to 85°C and supports low-voltage operation at 1.7 V–1.9 V, making it suitable where compact, low-voltage DDR2 memory is required on board-level designs.

Key Features

- Memory Organization and Capacity 512 Mbit total capacity arranged as 128M × 4 with 4 internal banks for concurrent operation and selectable burst lengths of 4 or 8.

- DDR2 Architecture DDR2 SDRAM core with 4n-bit prefetch, DLL to align DQ and DQS transitions with CK, and programmable CAS latency for flexible timing.

- Interface and Signaling Parallel memory interface with JEDEC-standard 1.8 V I/O (SSTL_18-compatible) and optional differential data strobe (DQS/DQS#) and duplicate output strobe (RDQS for x8).

- Power and Voltage Low-voltage operation: VDD and VDDQ nominally +1.8 V ±0.1 V (product spec listed supply 1.7 V–1.9 V), supporting reduced power consumption compared with higher-voltage memories.

- Timing and Performance Specified clock frequency 267 MHz and access time of 500 ps, with write cycle time (word page) of 15 ns; programmable timing options per DDR2 speed grades in the datasheet.

- System Reliability On-die termination (ODT), 64 ms/8,192-cycle refresh support and support for JEDEC clock jitter specifications to aid signal integrity and reliable operation.

- Package and Thermal Supplied in a 60-ball FBGA package (60-FBGA) for compact board-level integration; operating temperature range 0°C to 85°C (commercial).

- Standards and Compliance JEDEC-standard DDR2 signaling and RoHS compliant per the device datasheet.

Typical Applications

- Parallel DDR2 system memory Use as 512 Mbit parallel DDR2 SDRAM in systems that require a 128M × 4 memory organization and standard DDR2 signaling.

- Compact board-level memory The 60-FBGA footprint and 1.7 V–1.9 V supply make it suitable for compact PCB designs where low-voltage DDR2 is required.

- Commercial-temperature electronics Intended for commercial-temperature designs operating between 0°C and 85°C that need DDR2 performance and JEDEC-compliant signaling.

Unique Advantages

- Low-voltage operation: Supports VDD and VDDQ at approximately 1.8 V (1.7 V–1.9 V listed), enabling lower power consumption compared with higher-voltage memories.

- Flexible timing configuration: Programmable CAS latency and selectable burst lengths (4 or 8) allow timing adjustment to match system requirements.

- Signal integrity features: DLL alignment of DQ/DQS, on-die termination, and JEDEC clock jitter support help maintain data integrity at DDR2 speeds.

- Concurrent-bank operation: Four internal banks enable improved access concurrency for burst and interleaved access patterns.

- Compact packaging: 60-ball FBGA package supports dense board-level integration while retaining standard ballout options described in the device documentation.

- Standards compliance: JEDEC-standard 1.8 V I/O and RoHS-compliant device declaration (per datasheet) simplify system-level compliance planning.

Why Choose IC DRAM 512MBIT PAR 60FBGA?

The MT47H128M4CB-37E:B offers a commercially rated DDR2 SDRAM solution with a 512 Mbit capacity, low-voltage operation, and a compact 60-FBGA package. Its DDR2 feature set—programmable CAS latency, on-die termination, DLL alignment and four internal banks—provides flexible timing and signal integrity controls that match a range of board-level memory needs.

This device is appropriate for designers specifying parallel DDR2 memory in commercial-temperature electronics who require JEDEC-standard signaling, configurable timing, and a compact footprint. The documented electrical and timing characteristics support predictable integration and long-term design stability when used within the specified operating conditions.

Request a quote or submit an inquiry for MT47H128M4CB-37E:B to obtain pricing and availability information for your design and procurement needs.