MT53E512M64D2HJ-046 AUT:B TR

| Part Description |

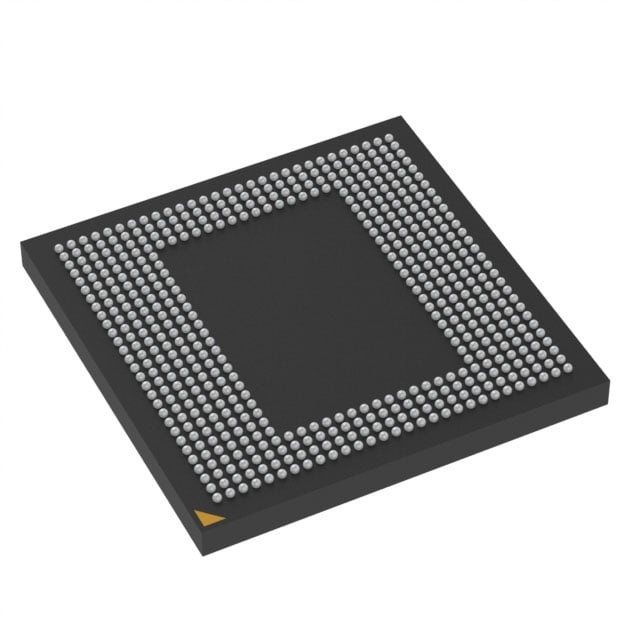

IC DRAM 32GBIT PAR 556WFBGA |

|---|---|

| Quantity | 403 Available (as of May 6, 2026) |

| Product Category | Memory |

|---|---|

| Manufacturer | Micron Technology Inc. |

| Manufacturing Status | Active |

| Manufacturer Standard Lead Time | 4 Weeks |

| Datasheet |

Specifications & Environmental

| Device Package | 556-WFBGA (12.4x12.4) | Memory Format | DRAM | Technology | SDRAM - Mobile LPDDR4X | ||

|---|---|---|---|---|---|---|---|

| Memory Size | 32 Gbit | Access Time | 3.5 ns | Grade | Automotive | ||

| Clock Frequency | 2.133 GHz | Voltage | 1.06V ~ 1.17V | Memory Type | Volatile | ||

| Operating Temperature | -40°C ~ 125°C (TC) | Write Cycle Time Word Page | 18 ns | Packaging | 556-TFBGA | ||

| Mounting Method | Volatile | Memory Interface | Parallel | Memory Organization | 512M x 64 | ||

| Moisture Sensitivity Level | N/A | RoHS Compliance | Unknown | REACH Compliance | REACH Unaffected | ||

| Qualification | AEC-Q100 | ECCN | N/A | HTS Code | N/A |

Overview of MT53E512M64D2HJ-046 AUT:B TR – IC DRAM 32GBIT PAR 556WFBGA

The MT53E512M64D2HJ-046 AUT:B TR is a high-density volatile DRAM device implemented in the LPDDR4X/LPDDR4 SDRAM architecture. It provides a 32 Gbit capacity in a 512M x 64 organization with a parallel memory interface optimized for high-bandwidth embedded systems.

Designed for automotive-grade applications, this device combines 2133 MHz clock operation (4266 Mb/s data rate per pin), low-voltage operation, and a compact 556-ball WFBGA package to deliver performance, power efficiency, and board-level integration for demanding environments.

Key Features

- Core / Architecture LPDDR4X/LPDDR4 SDRAM architecture with 16n prefetch and up to 8 internal banks per channel for concurrent operation.

- Memory Density & Organization 32 Gbit total capacity implemented as 512M x 64 (dual-die configuration D2) to support high-density memory designs.

- Performance 2.133 GHz clock rate (2133 MHz) with a data rate per pin of 4266 Mb/s and up to 8.5 GB/s per die x16 channel as specified in the device family information.

- Timing Fast access characteristics including an access time of 3.5 ns and write cycle time (word page) of 18 ns; programmable READ/WRITE latencies and selectable burst lengths (BL = 16, 32).

- Power & Voltage Ultra-low-voltage cores and I/O options: VDD2 = 1.06–1.17 V (1.10 V nominal) and VDDQ options including 0.57–0.65 V (0.60 V nominal) or 1.06–1.17 V, enabling lower power operation.

- System & Reliability Features Directed per-bank refresh, on-chip temperature sensor, partial-array self refresh (PASR), selectable output drive strength, and programmable ODT (VSS) termination.

- Interface & IO Parallel memory interface with single-data-rate CMD/ADR entry, bidirectional/differential data strobe per byte lane, and support for single-ended CK and DQS.

- Qualification & Temperature AEC-Q100 qualified with an operating temperature range of −40°C to 125°C (TC), targeting robust operation in temperature-critical applications.

- Package 556-ball TFBGA / WFBGA package (556-TFBGA, 12.4 × 12.4 mm) for compact, high-density board integration.

Typical Applications

- Automotive systems — Memory subsystem for automotive electronic modules where AEC-Q100 qualification and extended temperature operation are required.

- High-bandwidth embedded processors — Local DRAM for processors and SoCs requiring multi-gigabit-per-second data throughput per pin.

- Infotainment and telematics — Storage for frame buffers, multimedia processing, and data buffering in vehicle infotainment and telematics modules.

Unique Advantages

- High-density 32 Gbit capacity: Reduces the need for multiple devices by delivering 512M × 64 organization in a single package.

- High data-rate operation: 2133 MHz clock and 4266 Mb/s per-pin data rate support demanding bandwidth requirements.

- Low-voltage operation: VDD2 range of 1.06–1.17 V (and VDDQ low-voltage options) helps minimize power consumption in battery-sensitive or thermally constrained systems.

- Automotive qualification: AEC-Q100 qualification and −40°C to 125°C (TC) operating range enable use in temperature- and reliability-sensitive automotive electronics.

- Compact 556-ball package: 12.4 × 12.4 mm WFBGA footprint supports high-density PCB layouts and integration into space-constrained modules.

- System-friendly features: On-chip temperature sensor, directed per-bank refresh, and programmable latencies simplify memory management and thermal-aware operation.

Why Choose MT53E512M64D2HJ-046 AUT:B TR?

The MT53E512M64D2HJ-046 AUT:B TR positions itself as a high-density, high-bandwidth LPDDR4X/LPDDR4 memory device tailored for automotive and other demanding embedded systems. Its combination of 32 Gbit capacity, 4266 Mb/s per-pin data rates, low-voltage operation, and AEC-Q100 qualification addresses designs that require performance, efficiency, and extended temperature operation.

This device is appropriate for engineers designing compact, high-throughput memory subsystems—especially where automotive-grade qualification and thermal robustness are priorities. The Micron LPDDR4X product features and package options provide a verified integration path for long-term, high-reliability applications.

Request a quote or submit an RFQ to receive pricing and availability information for the MT53E512M64D2HJ-046 AUT:B TR.