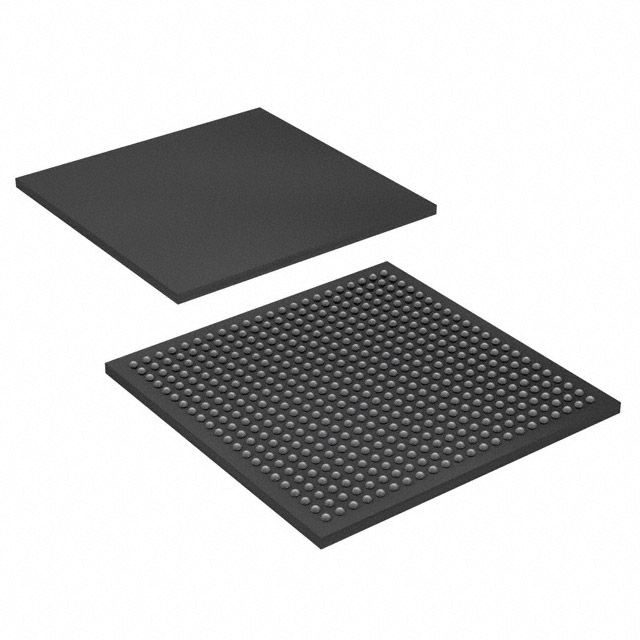

EP2S15F484C5N

| Part Description |

Stratix® II Field Programmable Gate Array (FPGA) IC 342 419328 15600 484-BBGA |

|---|---|

| Quantity | 894 Available (as of May 5, 2026) |

| Product Category | Field Programmable Gate Array (FPGA) |

|---|---|

| Manufacturer | Intel |

| Manufacturing Status | Obsolete |

| Manufacturer Standard Lead Time | RFQ |

| Datasheet |

Specifications & Environmental

| Device Package | 484-FBGA (23x23) | Grade | Commercial | Operating Temperature | 0°C – 85°C | ||

|---|---|---|---|---|---|---|---|

| Package / Case | 484-BBGA | Number of I/O | 342 | Voltage | 1.15 V - 1.25 V | ||

| Mounting Method | Surface Mount | RoHS Compliance | RoHS Compliant | REACH Compliance | REACH Unaffected | ||

| Moisture Sensitivity Level | 3 (168 Hours) | Number of LABs/CLBs | 780 | Number of Logic Elements/Cells | 15600 | ||

| Number of Gates | N/A | ECCN | 3A991D | HTS Code | 8542.39.0001 | ||

| Qualification | N/A | Total RAM Bits | 419328 |

Overview of EP2S15F484C5N – Stratix® II Field Programmable Gate Array (FPGA) IC 342 419328 15600 484-BBGA

The EP2S15F484C5N is a Stratix® II FPGA from Intel, delivering a programmable logic platform with dedicated on-chip resources for demanding embedded and signal-processing designs. The device combines 15,600 logic elements with substantial embedded memory and extensive I/O to support high-bandwidth logic, memory interfacing and high-speed I/O requirements.

Architectural elements documented for the Stratix II family—such as TriMatrix memory, digital signal processing blocks, multiple PLLs and a hierarchical clocking structure—give designers integrated resources for timing, DSP and interface tasks while maintaining a commercial-grade operating range and RoHS compliance.

Key Features

- Core Logic 15,600 logic elements provide the programmable capacity needed for complex control, glue-logic and custom processing functions.

- Embedded Memory Approximately 0.42 Mbits of on-chip RAM (419,328 total RAM bits) using the family’s TriMatrix memory architecture for efficient local storage and buffering.

- I/O and Interface Capability 342 user I/O pins with documented support for high-speed and advanced I/O standards, including double data rate interfaces and on-chip termination options.

- Clocking and Timing Integrated PLLs and hierarchical clock networks, including enhanced and fast PLL options, to support flexible clocking and multi-rate designs.

- On-Chip Tools & Configuration IEEE 1149.1 JTAG boundary-scan support and SignalTap II embedded logic analyzer capability enable in-system test, debug and configuration options.

- Package, Power and Thermal Surface-mount 484-BBGA (484-FBGA, 23 × 23) package, VCCINT supply range 1.15 V to 1.25 V, and commercial operating temperature range 0 °C to 85 °C.

- Reliability & Compliance Commercial-grade device with RoHS compliance.

Typical Applications

- High-speed signal processing Use the device’s digital signal processing blocks and substantial logic fabric for filter engines, FFTs and other DSP workloads.

- Memory interface controllers TriMatrix memory and documented external RAM interfacing support implementation of memory controllers, buffering and data-path management.

- Communications and I/O bridging Extensive I/O count and high-speed I/O support allow implementation of protocol bridges, packet processing and custom transceiver logic.

- Embedded control and glue logic Programmable logic elements and on-chip resources enable custom control, timing-critical glue logic and system-management functions.

Unique Advantages

- Substantial programmable capacity: 15,600 logic elements provide room for mid-range to complex FPGA designs without immediate need for larger devices.

- Integrated on-chip memory: Approximately 0.42 Mbits of embedded RAM reduces dependence on external memory for many buffering and local-storage needs.

- High I/O density: 342 I/O pins support multi-channel interfaces and complex board-level connectivity.

- Flexible clocking: Multiple PLLs and hierarchical clock networks enable multi-domain timing and flexible frequency management.

- In-system visibility and test: IEEE 1149.1 JTAG and SignalTap II support ease bring-up, debugging and field diagnostics.

- Commercial-grade and compliant: Surface-mount 484-BBGA packaging, 0 °C to 85 °C range and RoHS compliance meet typical commercial product requirements.

Why Choose EP2S15F484C5N?

The EP2S15F484C5N positions itself as a balanced Stratix® II solution for engineers who need sizeable programmable logic, embedded memory and robust I/O in a commercial-grade FPGA. Its combination of 15,600 logic elements, TriMatrix on-chip RAM and flexible clocking resources supports designs that require integrated DSP, interface controllers and high-speed data paths.

Backed by Intel’s Stratix II family documentation and configuration support (JTAG, SignalTap II), the device is suitable for teams building mid-complexity custom logic, memory interface controllers and I/O-intensive subsystems that benefit from on-chip debug and configuration capabilities.

Request a quote or submit a pricing inquiry for EP2S15F484C5N to check availability and lead times for your project.

Date Founded: 1968

Headquarters: Santa Clara, California, USA

Employees: 130,000+

Revenue: $54.23 Billion

Certifications and Memberships: ISO9001:2015, ISO14001:2015, ISO17025:2017, ISO27001:2022, ISO45001:2018, ISO50001:2018