EP2S15F484I4

| Part Description |

Stratix® II Field Programmable Gate Array (FPGA) IC 342 419328 15600 484-BBGA |

|---|---|

| Quantity | 319 Available (as of May 5, 2026) |

| Product Category | Field Programmable Gate Array (FPGA) |

|---|---|

| Manufacturer | Intel |

| Manufacturing Status | Obsolete |

| Manufacturer Standard Lead Time | RFQ |

| Datasheet |

Specifications & Environmental

| Device Package | 484-FBGA (23x23) | Grade | Industrial | Operating Temperature | -40°C – 100°C | ||

|---|---|---|---|---|---|---|---|

| Package / Case | 484-BBGA | Number of I/O | 342 | Voltage | 1.15 V - 1.25 V | ||

| Mounting Method | Surface Mount | RoHS Compliance | RoHS non-compliant | REACH Compliance | REACH Unaffected | ||

| Moisture Sensitivity Level | 3 (168 Hours) | Number of LABs/CLBs | 780 | Number of Logic Elements/Cells | 15600 | ||

| Number of Gates | N/A | ECCN | 3A991D | HTS Code | 8542.39.0001 | ||

| Qualification | N/A | Total RAM Bits | 419328 |

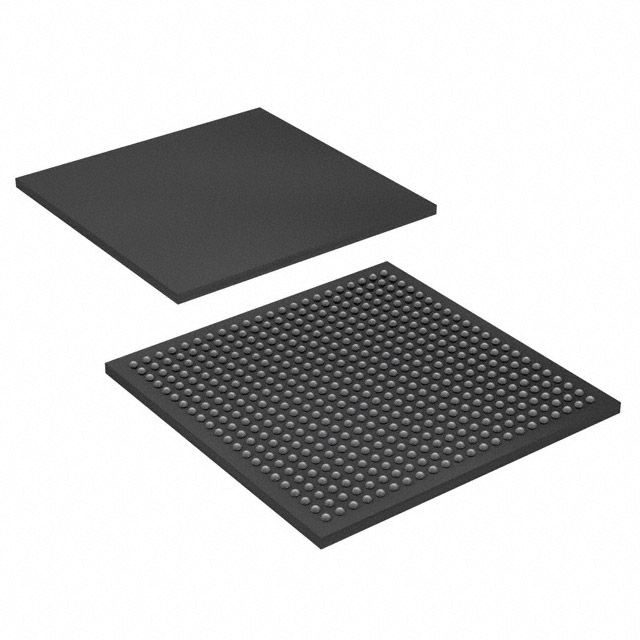

Overview of EP2S15F484I4 – Stratix® II Field Programmable Gate Array (FPGA) IC 342 I/Os 419,328 bits 15,600 LEs 484-BBGA

The EP2S15F484I4 is a Stratix II field programmable gate array (FPGA) from Intel, supplied in a 484-ball BGA package. It integrates 15,600 logic elements and approximately 0.42 Mbits of embedded memory (419,328 total RAM bits), delivering a compact, programmable platform for mid-density logic and system interfacing.

Designed for industrial-grade applications, this surface-mount device provides 342 I/O pins, a core supply range of 1.15 V to 1.25 V, and an operating temperature range of −40 °C to 100 °C, suitable for a range of embedded and industrial deployments.

Key Features

- High-density logic — 15,600 logic elements provide a robust fabric for implementing custom logic, state machines, and glue logic within a single device.

- Embedded memory — Approximately 0.42 Mbits of on-chip RAM (419,328 bits) supports FIFOs, small buffers, and local storage without immediate need for external RAM.

- Extensive I/O — 342 I/O pins enable broad interfacing options for peripherals, memory buses, and mixed-signal front-ends.

- Advanced chip architecture (series documentation) — Stratix II family documentation describes features such as PLLs and clock networks, high-speed I/O options, on-chip termination, and DSP blocks for timing, clocking, and signal processing use cases.

- Power — Core voltage supply range of 1.15 V to 1.25 V to match system power architectures.

- Industrial temperature rating — Specified operating range from −40 °C to 100 °C for reliable operation in demanding environments.

- Package & mounting — 484-ball BGA (supplier package listed as 484-FBGA, 23×23) in a surface-mount form factor for compact PCB integration.

- Environmental compliance — RoHS compliant, supporting current environmental manufacturing requirements.

Typical Applications

- Industrial control — Implement real-time logic, I/O aggregation, and protocol bridging while operating across industrial temperature ranges.

- High-speed interfaces — Use the device’s ample I/O count and Stratix II I/O architecture for bridging and buffering between high-pin-count subsystems.

- Signal processing glue logic — Combine logic elements and embedded RAM to implement custom preprocessing, buffering, or control around dedicated DSP systems.

- Embedded system integration — Consolidate control, interface, and timing functions into a single programmable device to reduce board-level complexity.

Unique Advantages

- Balanced logic and memory capacity: 15,600 logic elements combined with ~0.42 Mbits of embedded RAM enable mid-density designs without immediate external-memory dependence.

- High interface density: 342 I/Os give flexibility to connect multiple peripherals, buses, and external devices directly to the FPGA fabric.

- Industrial operating range: Rated from −40 °C to 100 °C for deployments that require extended-temperature reliability.

- Compact BGA footprint: 484-ball BGA (484-FBGA, 23×23) allows a high-pin-count device in a small PCB area to save system board real estate.

- Designed-in configurability: Stratix II family documentation highlights clocking, PLLs, high-speed I/O, and on-chip termination features that support flexible system timing and signal integrity strategies.

- RoHS compliant: Meets current lead-free manufacturing requirements for environmentally conscious production.

Why Choose EP2S15F484I4?

The EP2S15F484I4 positions itself as a practical Stratix II FPGA option for mid-density programmable logic needs where reliable industrial operation and extensive I/O are priorities. Its combination of 15,600 logic elements, substantial on-chip RAM, and 342 I/Os supports consolidation of control, interfacing, and data-path functions into a single device.

Engineers and procurement teams benefit from the Stratix II family documentation and device handbook for integration guidance and proven architecture elements such as clock networks, PLLs, and I/O options—helping reduce design iteration and accelerate development for industrial and embedded applications.

If you would like pricing, availability, or to request a formal quote for the EP2S15F484I4, submit a quotation request or contact sales to begin the procurement process.

Date Founded: 1968

Headquarters: Santa Clara, California, USA

Employees: 130,000+

Revenue: $54.23 Billion

Certifications and Memberships: ISO9001:2015, ISO14001:2015, ISO17025:2017, ISO27001:2022, ISO45001:2018, ISO50001:2018