EP2S15F672C4N

| Part Description |

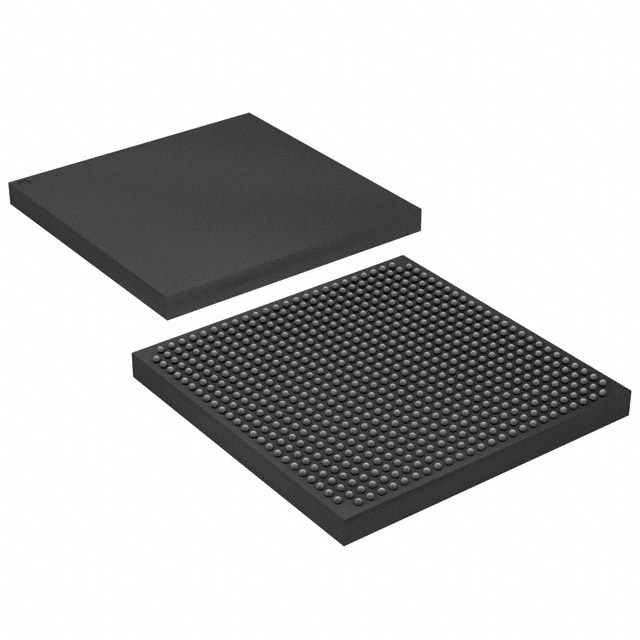

Stratix® II Field Programmable Gate Array (FPGA) IC 366 419328 15600 672-BBGA |

|---|---|

| Quantity | 1,906 Available (as of May 5, 2026) |

| Product Category | Field Programmable Gate Array (FPGA) |

|---|---|

| Manufacturer | Intel |

| Manufacturing Status | Obsolete |

| Manufacturer Standard Lead Time | RFQ |

| Datasheet |

Specifications & Environmental

| Device Package | 672-FBGA (27x27) | Grade | Commercial | Operating Temperature | 0°C – 85°C | ||

|---|---|---|---|---|---|---|---|

| Package / Case | 672-BBGA | Number of I/O | 366 | Voltage | 1.15 V - 1.25 V | ||

| Mounting Method | Surface Mount | RoHS Compliance | RoHS Compliant | REACH Compliance | REACH Unaffected | ||

| Moisture Sensitivity Level | 3 (168 Hours) | Number of LABs/CLBs | 780 | Number of Logic Elements/Cells | 15600 | ||

| Number of Gates | N/A | ECCN | 3A991D | HTS Code | 8542.39.0001 | ||

| Qualification | N/A | Total RAM Bits | 419328 |

Overview of EP2S15F672C4N – Stratix® II FPGA, 15,600 logic elements, 672-BBGA

The EP2S15F672C4N is a Stratix® II Field Programmable Gate Array (FPGA) in a 672-ball BGA package designed for commercial applications. It implements Stratix II architecture elements and provides a balance of programmable logic, embedded memory, and I/O resources for mid-range FPGA designs.

Typical use cases include digital signal processing, custom logic acceleration, and complex I/O interfacing where on-chip RAM, clock management and flexible I/O support are required. The device offers industry-standard surface-mount packaging and RoHS compliance for streamlined board-level integration.

Key Features

- Programmable Logic 15,600 logic elements provide the programmable fabric to implement control, data-path, and state-machine logic.

- Logic Array Blocks 780 logic array blocks (LABs) enabling structured placement of adaptive logic modules for efficient resource utilization.

- Embedded Memory Approximately 0.419 Mbits (419,328 bits) of on-chip RAM for FIFOs, packet buffers, and small data stores.

- I/O Capacity 366 I/O pins for flexible external interfacing and multiple bus connections on a single device.

- Power Supply Range Core supply range from 1.15 V to 1.25 V to match system power domains and specified operating conditions.

- Package & Mounting 672-ball BGA (supplier package: 672-FBGA, 27×27) in a surface-mount form factor for compact board integration.

- Operating Range Commercial temperature grade with an operating range of 0 °C to 85 °C, suitable for standard commercial environments.

- Standards & Reliability RoHS compliant to meet contemporary lead-free and environmental requirements.

- Stratix II Family Capabilities Stratix II architecture elements highlighted in the device handbook include configurable PLLs and clock networks, DSP blocks, on-chip termination and a comprehensive I/O structure for advanced timing and interface options.

- Configuration & Debug Support Series-level support includes JTAG boundary-scan and embedded logic analysis capabilities referenced in the Stratix II documentation.

Typical Applications

- Digital Signal Processing Use the device’s programmable logic and embedded memory to implement filters, FFTs, and custom DSP pipelines.

- High-Channel I/O Interfaces Leverage 366 I/O pins for multi-channel sensor arrays, parallel buses, or complex peripheral aggregation.

- Protocol Bridging & Custom Glue Logic Implement protocol converters, timing-adjusted interfaces, and glue logic between heterogeneous subsystems.

- Embedded Control Systems Apply the Stratix II fabric for state machines, motor-control logic, or real-time control tasks in commercial equipment.

Unique Advantages

- Balanced Logic and Memory: 15,600 logic elements paired with approximately 0.419 Mbits of on-chip RAM enable compact implementations of control and buffering in a single device, reducing board-level component count.

- Substantial I/O Density: 366 I/O pins allow high-connectivity designs without immediate need for external multiplexing or expanders.

- Flexible Power Integration: The defined core voltage range (1.15 V–1.25 V) supports integration into modern power architectures while maintaining specified device operation.

- Commercial Grade for Standard Environments: Rated for 0 °C–85 °C operation, this device fits production systems and customer designs targeting commercial temperature requirements.

- Compact Surface-Mount BGA: 672-BBGA (27×27) packaging delivers a high-pin-count solution in a compact footprint for dense PCB layouts.

- Series-Level Feature Set: Stratix II family capabilities such as PLLs, DSP blocks, on-chip termination, and configuration/debug infrastructure help accelerate design development and validation.

Why Choose EP2S15F672C4N?

The EP2S15F672C4N places Stratix II programmable fabric, embedded memory, and extensive I/O into a compact 672-ball BGA package targeted at commercial designs. It is suited for engineers who need mid-range logic density with flexible interfacing and the architectural capabilities documented for the Stratix II family.

Choosing this part provides a balanced platform for integrating logic, buffering and timing resources on a single device, enabling streamlined BOMs and conservative board real estate usage while meeting RoHS and commercial operating requirements.

Request a quote or submit a sales inquiry to obtain pricing and availability for the EP2S15F672C4N and to discuss lead times and order quantities.

Date Founded: 1968

Headquarters: Santa Clara, California, USA

Employees: 130,000+

Revenue: $54.23 Billion

Certifications and Memberships: ISO9001:2015, ISO14001:2015, ISO17025:2017, ISO27001:2022, ISO45001:2018, ISO50001:2018