EPF6016QC240-2

| Part Description |

FLEX 6000 Field Programmable Gate Array (FPGA) IC 199 1320 240-BFQFP |

|---|---|

| Quantity | 742 Available (as of May 5, 2026) |

| Product Category | Field Programmable Gate Array (FPGA) |

|---|---|

| Manufacturer | Intel |

| Manufacturing Status | Obsolete |

| Manufacturer Standard Lead Time | RFQ |

| Datasheet |

Specifications & Environmental

| Device Package | 240-PQFP (32x32) | Grade | Commercial | Operating Temperature | 0°C – 85°C | ||

|---|---|---|---|---|---|---|---|

| Package / Case | 240-BFQFP | Number of I/O | 199 | Voltage | 4.75 V - 5.25 V | ||

| Mounting Method | Surface Mount | RoHS Compliance | RoHS non-compliant | REACH Compliance | REACH Unaffected | ||

| Moisture Sensitivity Level | 6 (Time on Label) | Number of LABs/CLBs | 132 | Number of Logic Elements/Cells | 1320 | ||

| Number of Gates | 16000 | ECCN | 3A991D | HTS Code | 8542.39.0001 | ||

| Qualification | N/A |

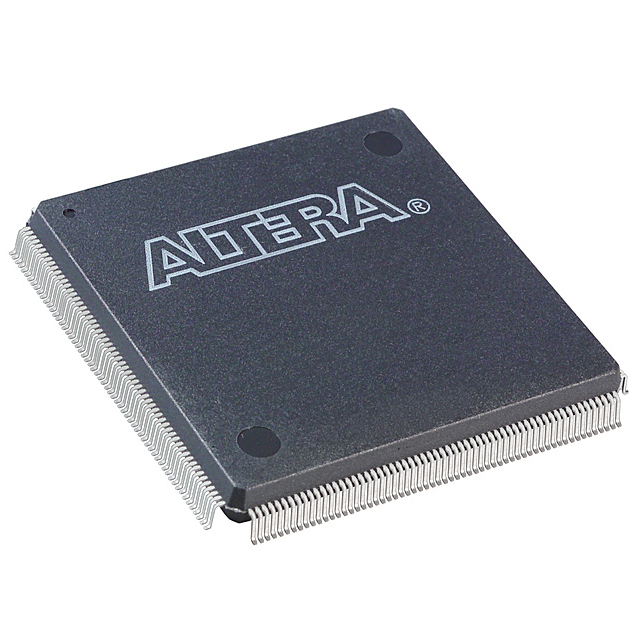

Overview of EPF6016QC240-2 – FLEX 6000 FPGA, 199 I/O, 1,320 Logic Elements, 240‑BFQFP

The EPF6016QC240-2 is a FLEX 6000 family field‑programmable gate array (FPGA) in a 240‑pin surface‑mount PQFP package. Based on a register‑rich, look‑up table (LUT) OptiFLEX architecture, this 5.0‑V device delivers reprogrammable mid‑density logic suitable for prototyping, system glue logic, and volume gate‑array alternatives.

With 1,320 logic elements (approximately 16,000 typical gates), up to 199 user I/O pins in the 240‑pin package, and features such as low‑skew clock distribution and in‑circuit reconfigurability, the device targets commercial applications that require flexible logic integration and field update capability while remaining RoHS compliant.

Key Features

- Core architecture Register‑rich, LUT‑based OptiFLEX architecture that optimizes device area efficiency for reprogrammable logic.

- Logic capacity 1,320 logic elements providing approximately 16,000 typical gates for mid‑density designs.

- I/O and output control 199 user I/O pins in the 240‑pin PQFP package with individual tri‑state output enable per pin and programmable output slew‑rate control to manage signal integrity and switching noise.

- Configuration and test Supports in‑circuit reconfiguration via external configuration device or controller and includes IEEE 1149.1 JTAG boundary‑scan test circuitry without consuming additional device logic.

- Interconnect and arithmetic support FastTrack interconnect with dedicated carry and cascade chains for efficient implementation of adders, counters and high‑fan‑in logic functions.

- Clocking and timing Built‑in low‑skew clock distribution tree and four low‑skew global paths for clock, clear, preset, or logic signals to simplify high‑performance timing designs.

- Power and voltage Designed for a 4.75 V to 5.25 V supply range; low standby current (typical specification less than 0.5 mA) for reduced idle power consumption.

- Package and mounting Surface‑mount 240‑BFQFP / 240‑PQFP (32x32) package, commercial grade, RoHS compliant, with an operating temperature range of 0 °C to 85 °C.

Typical Applications

- Prototype and design validation Use as a low‑cost, reprogrammable alternative to gate‑array prototyping to iterate designs quickly during development and testing.

- System glue logic and I/O bridging Bridge between subsystems and implement custom interface logic thanks to abundant I/O and programmable slew and output controls.

- In‑field reconfigurable systems Support for in‑circuit reconfiguration enables functional updates and feature changes in deployed equipment without device removal.

- Custom control and combinational logic Implement counters, adders and high‑fan‑in logic using dedicated carry and cascade chains for compact, high‑speed arithmetic blocks.

Unique Advantages

- Reprogrammability for rapid iteration: In‑circuit reconfiguration capability lets you update logic during prototyping or after deployment, reducing development cycles.

- Mid‑density logic in a compact package: 1,320 logic elements and about 16,000 typical gates provide substantial logic capacity in a 240‑pin surface‑mount form factor.

- High I/O count and control: Up to 199 user I/O pins with per‑pin tri‑state and slew‑rate control simplify high‑pin‑count interfacing without external glue logic.

- Testability and integration: Built‑in IEEE‑1149.1 JTAG boundary‑scan simplifies board‑level test while preserving device resources for user logic.

- Deterministic timing resources: Low‑skew clock tree and dedicated global paths reduce clock distribution complexity for synchronous designs.

- Commercial‑grade, RoHS compliant: Device and package meet commercial grade requirements and RoHS environmental compliance for standard commercial applications.

Why Choose EPF6016QC240-2?

The EPF6016QC240-2 combines OptiFLEX architecture and a practical balance of logic capacity, I/O density, and configuration features for commercial applications that need flexible, reprogrammable logic. Its dedicated arithmetic chains, low‑skew clocking, and comprehensive I/O controls make it suitable for system glue, interface bridging, and mid‑density custom logic implementations.

Designed for developers and procurement teams seeking a verified, RoHS‑compliant FLEX 6000 device in a 240‑pin PQFP package, this part offers a strong platform for designs that require field updates, board‑level testability, and predictable timing resources.

Request a quote or submit an inquiry to receive pricing and availability information for the EPF6016QC240-2.

Date Founded: 1968

Headquarters: Santa Clara, California, USA

Employees: 130,000+

Revenue: $54.23 Billion

Certifications and Memberships: ISO9001:2015, ISO14001:2015, ISO17025:2017, ISO27001:2022, ISO45001:2018, ISO50001:2018