5SGSMD4E1H29C2LN

| Part Description |

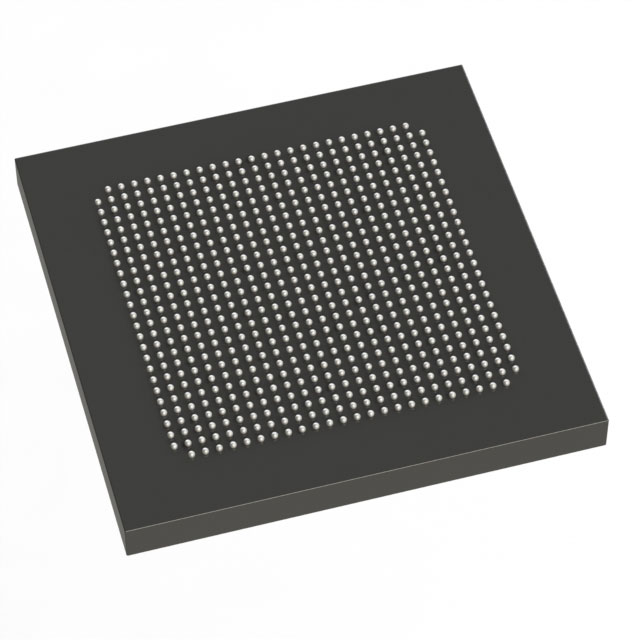

Stratix® V GS Field Programmable Gate Array (FPGA) IC 360 19456000 360000 780-BBGA, FCBGA |

|---|---|

| Quantity | 1,322 Available (as of May 5, 2026) |

| Product Category | Field Programmable Gate Array (FPGA) |

|---|---|

| Manufacturer | Intel |

| Manufacturing Status | Obsolete |

| Manufacturer Standard Lead Time | RFQ |

| Datasheet |

Specifications & Environmental

| Device Package | 780-HBGA (33x33) | Grade | Commercial | Operating Temperature | 0°C – 85°C | ||

|---|---|---|---|---|---|---|---|

| Package / Case | 780-BBGA, FCBGA | Number of I/O | 360 | Voltage | 820 mV - 880 mV | ||

| Mounting Method | Surface Mount | RoHS Compliance | RoHS Compliant | REACH Compliance | REACH Unknown | ||

| Moisture Sensitivity Level | 3 (168 Hours) | Number of LABs/CLBs | 135840 | Number of Logic Elements/Cells | 360000 | ||

| Number of Gates | N/A | ECCN | 3A001A2C | HTS Code | 8542.39.0001 | ||

| Qualification | N/A | Total RAM Bits | 19456000 |

Overview of 5SGSMD4E1H29C2LN – Stratix® V GS FPGA, approximately 360,000 logic elements

The 5SGSMD4E1H29C2LN is a Stratix V GS field programmable gate array (FPGA) in a 780‑ball BGA (FCBGA) package. It delivers a large logic capacity, substantial embedded memory, and extensive I/O for data‑intensive and DSP‑centric designs.

Targeted at high‑throughput and transceiver‑based applications, this GS‑variant device provides an architecture optimized for variable‑precision digital signal processing and integrated high‑speed transceiver capability as described for the Stratix V GS family.

Key Features

- Logic Capacity — Approximately 360,000 logic elements to implement complex custom logic and control functions.

- Embedded Memory — Approximately 19.456 Mbits of on‑chip RAM for buffering, lookup tables, and data staging.

- I/O Density — 360 user I/O pins to support broad peripheral and high‑speed interface requirements.

- DSP Resources (family feature) — Stratix V GS family includes an abundance of variable‑precision DSP blocks suitable for high‑precision DSP workflows; series documentation notes support for large counts of 18×18 and 27×27 multipliers.

- Integrated Transceivers (family feature) — GS devices in the Stratix V family offer integrated transceivers with 14.1‑Gbps data rate capability for backplane and optical interfaces.

- Power — Core supply specified from 820 mV to 880 mV to match low‑voltage core domains.

- Package & Mounting — 780‑ball BGA (FCBGA), supplier package 780‑HBGA (33×33), surface‑mount package for compact, board‑level integration.

- Temperature & Grade — Commercial grade with an operating range of 0 °C to 85 °C.

- Compliance — RoHS compliant.

Typical Applications

- High‑density DSP systems — Implements complex, variable‑precision DSP pipelines where abundant DSP blocks and on‑chip memory reduce external memory traffic.

- Optical and backplane interfaces — GS family transceiver capability supports high‑speed serial links for 40G/100G class transport and related applications.

- Data‑intensive networking — Large logic and memory resources enable packet processing, traffic management, and protocol acceleration functions.

- High‑performance computing and broadcast — Combines dense logic, DSP resources, and many I/O to implement compute‑intensive, latency‑sensitive workloads.

Unique Advantages

- Substantial logic capacity: Approximately 360,000 logic elements let you map large finite state machines, control logic and datapaths on a single device.

- Significant on‑chip memory: Approximately 19.456 Mbits of embedded RAM reduces dependence on external memories and improves throughput for buffering and lookups.

- High I/O count: 360 I/O pins provide flexibility for multi‑lane interfaces and broad peripheral connectivity without extra bridging components.

- DSP and transceiver‑focused architecture: As a Stratix V GS device, it targets DSP‑centric, transceiver‑based applications—helpful for designs needing integrated multiplier resources and high‑speed serial links.

- Compact surface‑mount BGA: The 780‑ball FCBGA package enables high‑density PCB integration while maintaining thermal and routing options for complex board designs.

- Commercial‑grade availability: Specified for 0 °C to 85 °C operation and RoHS compliant for standard commercial deployments.

Why Choose 5SGSMD4E1H29C2LN?

The 5SGSMD4E1H29C2LN pairs the Stratix V GS family architecture with device‑level resources suited for DSP‑heavy, transceiver‑enabled, and data‑intensive applications. Its combination of approximately 360,000 logic elements, roughly 19.456 Mbits of embedded RAM, and 360 I/O pins supports large, integrated designs that benefit from on‑chip memory and dense logic fabrics.

This device is appropriate for engineering teams building communication, networking, broadcast, or compute accelerators that require family‑level DSP and transceiver capabilities together with a commercial‑grade package and mounting for production assemblies.

Request a quote or submit your requirements to receive pricing and availability for the 5SGSMD4E1H29C2LN.

Date Founded: 1968

Headquarters: Santa Clara, California, USA

Employees: 130,000+

Revenue: $54.23 Billion

Certifications and Memberships: ISO9001:2015, ISO14001:2015, ISO17025:2017, ISO27001:2022, ISO45001:2018, ISO50001:2018