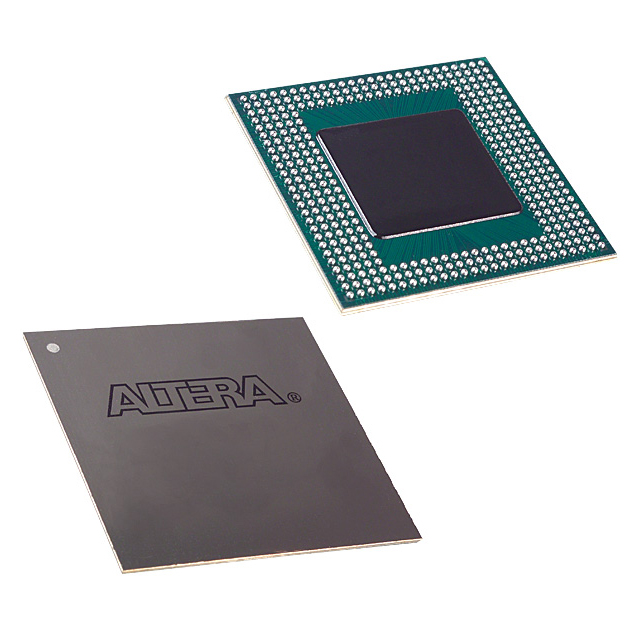

EP20K200EBC652-1

| Part Description |

APEX-20KE® Field Programmable Gate Array (FPGA) IC 376 106496 8320 652-BGA |

|---|---|

| Quantity | 786 Available (as of May 5, 2026) |

| Product Category | Field Programmable Gate Array (FPGA) |

|---|---|

| Manufacturer | Intel |

| Manufacturing Status | Obsolete |

| Manufacturer Standard Lead Time | RFQ |

| Datasheet |

Specifications & Environmental

| Device Package | 652-BGA (45x45) | Grade | Commercial | Operating Temperature | 0°C – 85°C | ||

|---|---|---|---|---|---|---|---|

| Package / Case | 652-BGA | Number of I/O | 376 | Voltage | 1.71 V - 1.89 V | ||

| Mounting Method | Surface Mount | RoHS Compliance | Unknown | REACH Compliance | REACH Unaffected | ||

| Moisture Sensitivity Level | 3 (168 Hours) | Number of LABs/CLBs | 832 | Number of Logic Elements/Cells | 8320 | ||

| Number of Gates | 526000 | ECCN | 3A001A2A | HTS Code | 8542.39.0001 | ||

| Qualification | N/A | Total RAM Bits | 106496 |

Overview of EP20K200EBC652-1 – APEX-20KE® Field Programmable Gate Array (FPGA) IC, 652‑BGA

The EP20K200EBC652-1 is an APEX‑20KE family FPGA from Intel, offering 526,000 system gates in a 652‑BGA (45×45) surface‑mount package. It integrates a MultiCore architecture with lookup‑table (LUT) logic and embedded system blocks (ESBs), delivering a compact programmable platform with 8,320 logic elements and approximately 0.106 Mbits of on‑chip RAM for control, buffering, and memory‑intensive functions.

Designed for commercial applications, the device supports 376 user I/O pins and operates from a VCCINT supply in the 1.71 V to 1.89 V range with an ambient operating temperature of 0 °C to 85 °C. It is RoHS‑compliant and intended for designs that require significant integration of logic, memory, and flexible I/O in a single FPGA package.

Key Features

- APEX MultiCore Architecture Combines LUT logic, product‑term logic, and embedded memory blocks (ESBs) to support register‑intensive and combinatorial functions within the same fabric.

- Logic Capacity 8,320 logic elements and a system gate count of 526,000 provide substantial programmable logic resources for complex designs.

- Embedded Memory Approximately 106,496 bits of on‑chip RAM implemented in ESBs for FIFOs, dual‑port RAM, and CAM functions.

- I/O and Interface Flexibility 376 user I/O pins with MultiVolt I/O support to interface with a variety of voltage domains and standards; includes programmable clamp and output slew‑rate control.

- Clock and Timing Integrated clock management features from the APEX‑20K family such as multiple PLLs, global clock signals, and low‑skew clock trees for predictable timing (family features documented in the APEX‑20K datasheet).

- Power and Supply Internal supply operation in the 1.71 V to 1.89 V range and design features in the APEX‑20K family for low‑power operation and programmable power‑saving modes in ESBs.

- Package and Mounting 652‑BGA (45×45) package, surface‑mount mounting type suitable for high‑density PCB layouts.

- Commercial Temperature Grade Specified for 0 °C to 85 °C operation suitable for commercial applications.

- Regulatory RoHS‑compliant.

Typical Applications

- High‑speed memory controllers Use the embedded RAM and ESB structures to implement DDR SDRAM or ZBT SRAM interface logic and buffering.

- Bus‑based systems and I/O bridging Leverage MultiVolt I/O and PCI‑compatible features from the APEX‑20K family to implement PCI/PCI‑X interfacing and bus adaptation.

- Embedded system integration SOPC‑style integration and ESB resources enable on‑chip implementation of FIFOs, dual‑port RAM, and control logic for embedded applications.

- High‑throughput serial/deserializer links Family LVDS and high‑speed I/O capabilities support implementations that require fast differential signaling and channelized data transfer.

Unique Advantages

- Substantial programmable logic in a compact package: 8,320 logic elements and 526,000 system gates in a 652‑BGA provide dense integration for complex designs without excessive board area.

- Embedded memory tailored for system functions: ESBs deliver approximately 0.106 Mbits of on‑chip RAM suitable for FIFOs, buffering, and dual‑port memory use cases.

- Flexible I/O and voltage compatibility: 376 user I/O pins with MultiVolt support and programmable I/O features simplify interfacing to multiple voltage domains and legacy standards.

- Deterministic clocking features: APEX‑20K family clock management capabilities (multiple PLLs, global clocks, low‑skew clock trees) help meet timing requirements for synchronous systems.

- Commercial‑grade readiness: Rated for 0 °C to 85 °C operation and RoHS‑compliant, making it suitable for a wide range of commercial electronic products.

- Surface‑mount 652‑BGA (45×45): Enables high‑pin‑count, high‑density board designs while maintaining manufacturability for SMT assembly.

Why Choose EP20K200EBC652-1?

The EP20K200EBC652-1 positions itself as a highly integrated FPGA option within the APEX‑20KE family, combining a significant logic element count, embedded memory resources, and broad I/O flexibility in a single 652‑BGA package. It is a practical choice for designers who need to consolidate controller, memory‑interface, and I/O glue logic into one programmable device while maintaining commercial temperature and RoHS compliance.

This device is well suited for teams developing memory‑centric or bus‑centric systems, embedded processing solutions, and high‑throughput I/O paths that benefit from the APEX‑20K family’s clocking and ESB capabilities. Backed by Intel’s APEX‑20K documentation and family‑level features, it provides a predictable platform for scalable designs.

Request a quote or submit an inquiry to receive pricing, availability, and procurement details for the EP20K200EBC652-1.

Date Founded: 1968

Headquarters: Santa Clara, California, USA

Employees: 130,000+

Revenue: $54.23 Billion

Certifications and Memberships: ISO9001:2015, ISO14001:2015, ISO17025:2017, ISO27001:2022, ISO45001:2018, ISO50001:2018