EP20K30EFC144-1N

| Part Description |

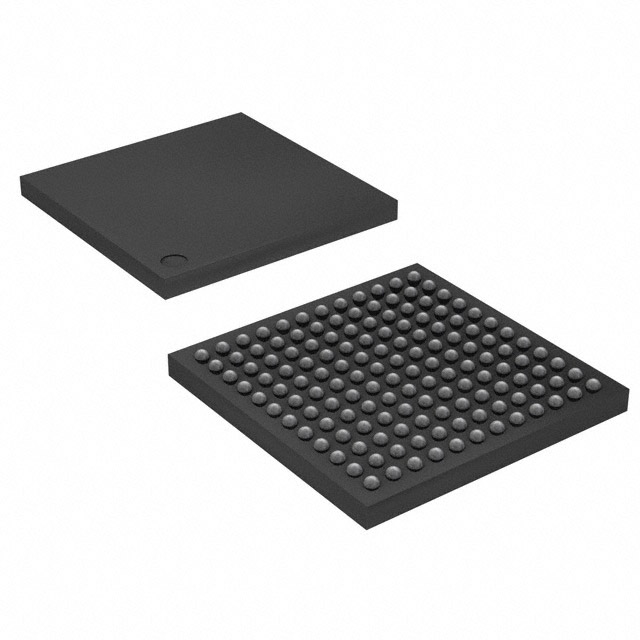

APEX-20KE® Field Programmable Gate Array (FPGA) IC 93 24576 1200 144-BGA |

|---|---|

| Quantity | 1,044 Available (as of May 5, 2026) |

| Product Category | Field Programmable Gate Array (FPGA) |

|---|---|

| Manufacturer | Intel |

| Manufacturing Status | Obsolete |

| Manufacturer Standard Lead Time | RFQ |

| Datasheet |

Specifications & Environmental

| Device Package | 144-FBGA (13x13) | Grade | Commercial | Operating Temperature | 0°C – 85°C | ||

|---|---|---|---|---|---|---|---|

| Package / Case | 144-BGA | Number of I/O | 93 | Voltage | 1.71 V - 1.89 V | ||

| Mounting Method | Surface Mount | RoHS Compliance | Unknown | REACH Compliance | REACH Unaffected | ||

| Moisture Sensitivity Level | 3 (168 Hours) | Number of LABs/CLBs | 120 | Number of Logic Elements/Cells | 1200 | ||

| Number of Gates | 113000 | ECCN | 3A001A2A | HTS Code | 8542.39.0001 | ||

| Qualification | N/A | Total RAM Bits | 24576 |

Overview of EP20K30EFC144-1N – APEX-20KE FPGA, 1.8 V Internal, 144-FBGA, 1,200 Logic Elements

The EP20K30EFC144-1N is an APEX-20KE® field programmable gate array (FPGA) IC from Intel, designed for commercial embedded logic applications. It implements the APEX 20K family’s MultiCore architecture—combining look-up-table (LUT) logic, product-term logic, and embedded system blocks (ESBs)—to deliver a compact, programmable platform for custom logic, memory functions and high-speed I/O.

Targeted use cases include embedded systems, high-speed interface controllers and compact programmable logic implementations where a balance of logic density, on-chip RAM and flexible I/O is required.

Key Features

- MultiCore architecture Integrates LUT logic, product-term logic and embedded memory (ESB) enabling register‑intensive and combinatorial functions within the APEX 20K family architecture.

- Logic resources Approximately 1,200 logic elements and a maximum system gate count of 113,000 provide a compact logic fabric for control, glue-logic and custom processing tasks.

- Embedded memory (ESBs) 24,576 total RAM bits available for on-chip FIFOs, dual-port RAM, or CAM-style implementations, enabling efficient local buffering and state storage.

- I/O and interface capability 93 user I/O pins with MultiVolt I/O interface support (1.8 V, 2.5 V, 3.3 V, 5.0 V) plus family-level support for PCI 3.3-V operation, DDR SDRAM and ZBT SRAM interfaces, LVDS channels and other advanced standards.

- Clock management Flexible on-chip clocking with up to four PLLs, low‑skew clock tree and up to eight global clock signals, plus programmable features such as ClockLock, ClockBoost and ClockShift for phase and delay control.

- Low-power design Designed for low-power operation with a nominal internal supply around 1.8 V (device supply range 1.71–1.89 V) and ESB power-saving options.

- Package and thermal Surface-mount 144-FBGA (13 × 13) package; commercial-grade operating temperature 0 °C to 85 °C.

- Compliance RoHS compliant.

Typical Applications

- Embedded systems Implement control logic, protocol bridging and local buffering using on-chip LUTs and ESBs to reduce external components.

- Memory interface controllers Serve as configurable controllers and sequencers for DDR SDRAM and ZBT SRAM thanks to the family’s external memory support and flexible I/O.

- High-speed communications Leverage LVDS channels and high-performance I/O options for serial links, data aggregation and interface conversion.

- SOPC and system integration Use the APEX 20K family’s system-on-a-programmable-chip (SOPC) integration capabilities to consolidate logic, memory and interface functions on a single device.

Unique Advantages

- Highly integrated architecture: Combines LUTs, product-term logic and embedded system blocks to implement both register‑intensive and memory‑based functions on one device, reducing board-level complexity.

- Balanced resources for compact designs: Around 1,200 logic elements with 24,576 bits of on-chip RAM provide a practical mix of logic and local memory for mid-density applications.

- Flexible I/O support: MultiVolt I/O capability and family-level support for PCI, DDR and LVDS let you interface with a wide range of external devices and memory technologies.

- Deterministic clocking: Multiple PLLs, a low‑skew clock tree and programmable clock features simplify timing management for synchronous systems.

- Commercial-grade, surface-mount packaging: 144-FBGA (13×13) package and 0 °C to 85 °C operating range support typical commercial embedded environments while minimizing PCB area.

Why Choose EP20K30EFC144-1N?

The EP20K30EFC144-1N positions itself as a compact, commercially graded FPGA option within the APEX 20K family, offering a practical combination of logic elements, embedded RAM and flexible I/O in a 144-FBGA package. It is well suited for designers who need on-chip FIFOs and memory-backed logic, deterministic clocking, and MultiVolt I/O capability in space-constrained designs.

Choosing this device brings the advantages of the APEX 20K device family’s architectural features—LUT/product-term/ESB integration and flexible clocking—giving design teams a scalable, supported platform for mid-density programmable logic tasks.

Request a quote or submit an inquiry to receive pricing and availability information for the EP20K30EFC144-1N.

Date Founded: 1968

Headquarters: Santa Clara, California, USA

Employees: 130,000+

Revenue: $54.23 Billion

Certifications and Memberships: ISO9001:2015, ISO14001:2015, ISO17025:2017, ISO27001:2022, ISO45001:2018, ISO50001:2018