EP2C50F484C7

| Part Description |

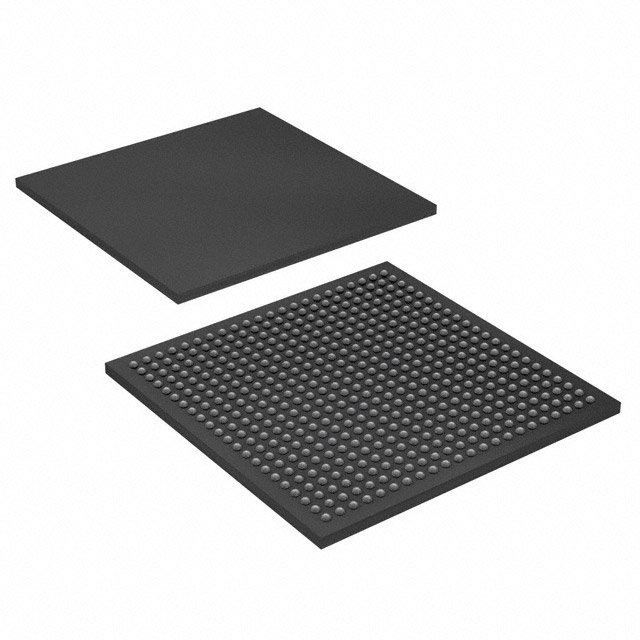

Cyclone® II Field Programmable Gate Array (FPGA) IC 294 594432 50528 484-BGA |

|---|---|

| Quantity | 763 Available (as of May 6, 2026) |

| Product Category | Field Programmable Gate Array (FPGA) |

|---|---|

| Manufacturer | Intel |

| Manufacturing Status | Active |

| Manufacturer Standard Lead Time | 26 Weeks |

| Datasheet |

Specifications & Environmental

| Device Package | 484-FBGA (23x23) | Grade | Commercial | Operating Temperature | 0°C – 85°C | ||

|---|---|---|---|---|---|---|---|

| Package / Case | 484-BGA | Number of I/O | 294 | Voltage | 1.15 V - 1.25 V | ||

| Mounting Method | Surface Mount | RoHS Compliance | RoHS non-compliant | REACH Compliance | REACH Unaffected | ||

| Moisture Sensitivity Level | 3 (168 Hours) | Number of LABs/CLBs | 3158 | Number of Logic Elements/Cells | 50528 | ||

| Number of Gates | N/A | ECCN | 3A991D | HTS Code | 8542.39.0001 | ||

| Qualification | N/A | Total RAM Bits | 594432 |

Overview of EP2C50F484C7 – Cyclone® II Field Programmable Gate Array (FPGA), 50528 LEs, 484-BGA

The EP2C50F484C7 is an Intel Cyclone II FPGA device built on the Cyclone II architecture. It delivers 50,528 logic elements, approximately 0.59 Mbits of embedded memory, and up to 294 user I/O in a 484-ball FBGA package for surface-mount applications.

Designed for low-cost embedded processing and DSP-oriented designs, this commercial-grade, RoHS-compliant FPGA combines on-chip memory, embedded multipliers, flexible I/O support and series-level clocking and configuration features to address a range of mid-density programmable logic applications.

Key Features

- Core Logic 50,528 logic elements (cells) organized per the Cyclone II architecture to implement combinational and sequential logic.

- Embedded Memory Approximately 0.59 Mbits of on-chip RAM (594,432 total RAM bits) for FIFOs, buffers, and local storage.

- Arithmetic & DSP Support Cyclone II series-level embedded multipliers and DSP-oriented features to accelerate arithmetic-intensive functions.

- Clocking & Configuration Series architecture includes global clock networks and PLL support for flexible clock management and multiple configuration options.

- I/O and Packaging 294 user I/O pins in a 484-FBGA (23×23) package; surface-mount mounting type supports multi-voltage I/O standards and programmable I/O features described in the Cyclone II device handbook.

- Power & Temperature Core voltage supply range of 1.15 V to 1.25 V and commercial operating temperature range of 0 °C to 85 °C.

- Reliability & Compliance RoHS-compliant commercial-grade device with series-level support for JTAG boundary scan, hot-socketing behavior, and power-on reset circuitry outlined in the Cyclone II handbook.

Typical Applications

- Low-Cost Embedded Processing — Implement embedded control, glue logic, and peripheral interfaces where a mid-density FPGA with on-chip RAM and configurable I/O is required.

- Low-Cost DSP Solutions — Deploy arithmetic and signal-processing blocks using the Cyclone II embedded multipliers and on-chip memory for filtering, accumulation, and intermediate data storage.

- External Memory Interfacing — Use dedicated I/O features and the device’s memory/interface resources for memory controllers, buffering, and protocol conversion tasks.

- High-Speed I/O Prototyping — Leverage the device’s series-level high-speed differential interface support and programmable I/O drive features for prototyping serial links and mixed-signal interfaces.

Unique Advantages

- Highly integrated mid-density FPGA: 50,528 logic elements and embedded RAM reduce external component count for many embedded and DSP functions.

- Flexible I/O capacity: 294 user I/Os in a 484-FBGA package provide broad signal connectivity for interfaces and peripheral expansion.

- Commercial-ready operating range: Rated for 0 °C to 85 °C and RoHS-compliant, suitable for mainstream commercial product designs.

- Low-voltage core support: Core supply between 1.15 V and 1.25 V enables designs targeting lower core voltage domains consistent with Cyclone II device requirements.

- Series-level clocking and DSP features: Built on Cyclone II architecture with global clock networks, PLLs and embedded multipliers to simplify timing and arithmetic implementations.

- Compact, surface-mount package: 484-FBGA (23×23) package supports high I/O density while optimizing PCB area for compact systems.

Why Choose EP2C50F484C7?

The EP2C50F484C7 places a robust set of Cyclone II series features—50,528 logic elements, embedded memory, DSP-oriented blocks, and a high I/O count—into a compact 484-FBGA package. This combination makes it well-suited to designers who need a mid-density, cost-conscious FPGA with on-chip resources for embedded processing, signal processing, and interface bridging.

With its commercial operating range, RoHS compliance, and Cyclone II family architecture, EP2C50F484C7 offers a balance of integration, configurability, and series-level tooling and documentation that supports scalable development and long-term design maintenance.

Request a quote or submit an inquiry to check availability, lead times, and pricing for the EP2C50F484C7. Our team can provide the information you need to move your design forward.

Date Founded: 1968

Headquarters: Santa Clara, California, USA

Employees: 130,000+

Revenue: $54.23 Billion

Certifications and Memberships: ISO9001:2015, ISO14001:2015, ISO17025:2017, ISO27001:2022, ISO45001:2018, ISO50001:2018