EP2S30F484C5

| Part Description |

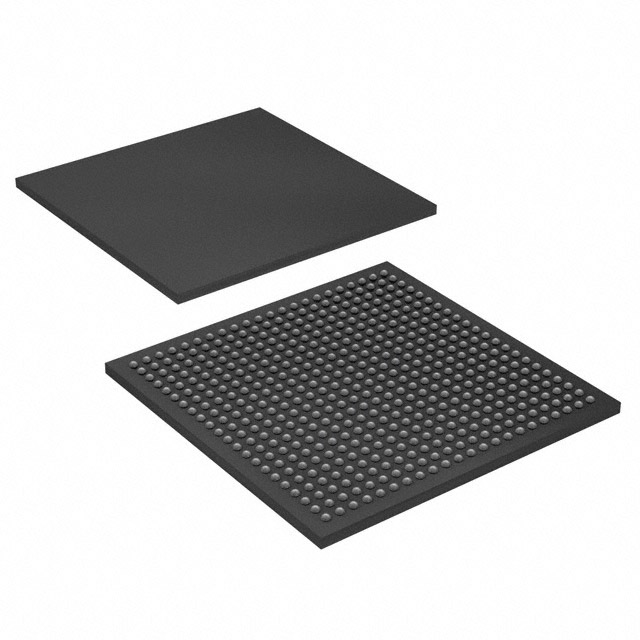

Stratix® II Field Programmable Gate Array (FPGA) IC 342 1369728 33880 484-BBGA |

|---|---|

| Quantity | 1,484 Available (as of May 5, 2026) |

| Product Category | Field Programmable Gate Array (FPGA) |

|---|---|

| Manufacturer | Intel |

| Manufacturing Status | Obsolete |

| Manufacturer Standard Lead Time | RFQ |

| Datasheet |

Specifications & Environmental

| Device Package | 484-FBGA (23x23) | Grade | Commercial | Operating Temperature | 0°C – 85°C | ||

|---|---|---|---|---|---|---|---|

| Package / Case | 484-BBGA | Number of I/O | 342 | Voltage | 1.15 V - 1.25 V | ||

| Mounting Method | Surface Mount | RoHS Compliance | RoHS non-compliant | REACH Compliance | REACH Unaffected | ||

| Moisture Sensitivity Level | 3 (168 Hours) | Number of LABs/CLBs | 1694 | Number of Logic Elements/Cells | 33880 | ||

| Number of Gates | N/A | ECCN | 3A991D | HTS Code | 8542.39.0001 | ||

| Qualification | N/A | Total RAM Bits | 1369728 |

Overview of EP2S30F484C5 – Stratix® II FPGA, 33,880 logic elements, 484‑BBGA

The EP2S30F484C5 is a Stratix II Field Programmable Gate Array (FPGA) provided in a 484‑ball BGA (484‑FBGA, 23×23) surface‑mount package. It delivers a high‑density programmable fabric driven by Stratix II architecture building blocks such as adaptive logic modules, dedicated DSP circuitry and advanced clocking resources.

Designed for complex digital logic and signal‑processing designs, the device targets applications that require substantial on‑chip memory, a large I/O count, and flexible high‑speed I/O and clocking options while operating within a commercial temperature range.

Key Features

- Programmable Logic Density — 33,880 logic elements (cells) for implementing substantial custom logic and state machines.

- Embedded Memory — Approximately 1.37 Mbits of on‑chip RAM (1,369,728 total RAM bits) to support buffering, FIFOs and local storage for DSP and control logic.

- High I/O Count — 342 user I/O pins to support wide bus interfaces, parallel peripherals and multi‑channel connectivity.

- Dedicated DSP & Clocking Blocks — Stratix II architecture includes DSP resources and enhanced PLL/clock networks for deterministic timing and signal processing use cases (as detailed in the device handbook).

- Advanced I/O Support — On‑chip termination, multi‑voltage I/O options and high‑speed differential I/O support enable robust interfacing with external memory and high‑speed links (features described in the handbook).

- Configuration & Debug — IEEE‑1149.1 JTAG boundary‑scan support and embedded logic analysis options (SignalTap II) for in‑system debugging and validation.

- Power & Operating Range — Core voltage supply specified at 1.15 V to 1.25 V and commercial operating temperature from 0 °C to 85 °C.

- Package & Compliance — 484‑FBGA (23×23) surface‑mount package; RoHS compliant and supplied in a commercial grade.

Typical Applications

- High‑performance digital signal processing — Use the on‑chip DSP blocks, embedded RAM and dense logic elements to implement filters, transforms and real‑time processing chains.

- High‑speed communications — Leverage the device’s high I/O count, differential I/O support and clocking resources for protocol bridging, packet processing or transceiver interface logic.

- Prototyping and custom logic emulation — Deploy the Stratix II fabric to prototype ASIC functions or accelerate development of complex control and data‑path logic.

- Data acquisition and instrumentation — Combine abundant I/Os and on‑chip memory to capture, preprocess and buffer multi‑channel sensor or measurement data.

Unique Advantages

- High integration density: 33,880 logic elements reduce external glue logic and simplify system partitioning for complex designs.

- Substantial embedded memory: Approximately 1.37 Mbits of on‑chip RAM supports deep buffering and local storage close to processing logic.

- Extensive I/O capability: 342 I/Os enable wide parallel interfaces and multi‑channel connectivity without extensive external multiplexing.

- Architectural building blocks: Stratix II features such as DSP blocks, TriMatrix memory and PLL/clock networks (documented in the device handbook) provide targeted resources for signal processing and timing‑sensitive designs.

- Commercial operating range: Rated for 0 °C to 85 °C, aligning with a wide range of commercial and enterprise applications.

- Design visibility and testability: JTAG boundary‑scan and embedded logic analysis capabilities simplify bring‑up, verification and in‑system debug.

Why Choose EP2S30F484C5?

The EP2S30F484C5 combines ample logic capacity, significant on‑chip memory and a large I/O complement within the Stratix II architecture, making it well suited to designs that require integrated DSP resources, flexible clocking and robust I/O options. Its documented architecture elements—adaptive logic modules, DSP blocks, TriMatrix memory and enhanced PLLs—help designers map complex algorithms and timing‑sensitive functions into a single device.

This device is appropriate for teams and projects that need a commercially graded, RoHS‑compliant FPGA with proven configuration and debug options and a compact 484‑FBGA footprint. Its combination of resources supports scalable development paths and streamlined board‑level integration.

Request a quote or submit a pricing and availability inquiry to receive lead‑time and procurement details for EP2S30F484C5.

Date Founded: 1968

Headquarters: Santa Clara, California, USA

Employees: 130,000+

Revenue: $54.23 Billion

Certifications and Memberships: ISO9001:2015, ISO14001:2015, ISO17025:2017, ISO27001:2022, ISO45001:2018, ISO50001:2018