10AX032E1F29E1HG

| Part Description |

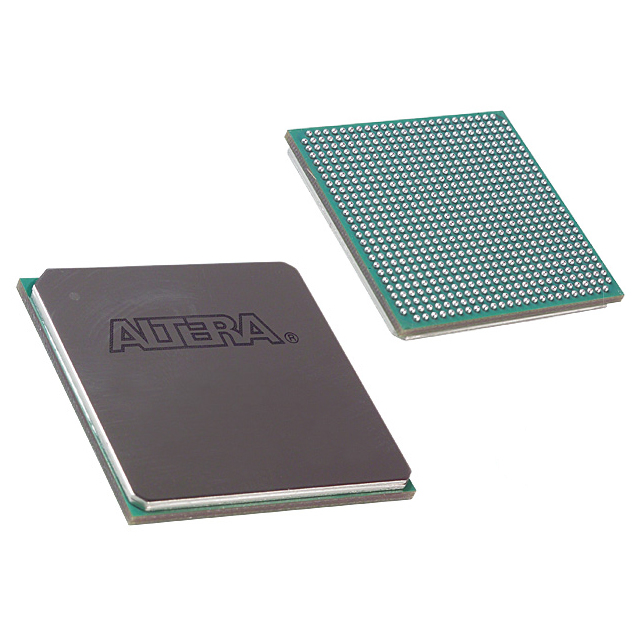

Arria 10 GX Field Programmable Gate Array (FPGA) IC 360 21040128 320000 780-BBGA, FCBGA |

|---|---|

| Quantity | 18 Available (as of May 5, 2026) |

| Product Category | Field Programmable Gate Array (FPGA) |

|---|---|

| Manufacturer | Intel |

| Manufacturing Status | Active |

| Manufacturer Standard Lead Time | 13 Weeks |

| Datasheet |

Specifications & Environmental

| Device Package | 780-FBGA (29x29) | Grade | Extended | Operating Temperature | 0°C – 100°C | ||

|---|---|---|---|---|---|---|---|

| Package / Case | 780-BBGA, FCBGA | Number of I/O | 360 | Voltage | 870 mV - 980 mV | ||

| Mounting Method | Surface Mount | RoHS Compliance | RoHS Compliant | REACH Compliance | REACH Unaffected | ||

| Moisture Sensitivity Level | 3 (168 Hours) | Number of LABs/CLBs | 119900 | Number of Logic Elements/Cells | 320000 | ||

| Number of Gates | N/A | ECCN | 5A002A1 | HTS Code | 8542.39.0001 | ||

| Qualification | N/A | Total RAM Bits | 21040128 |

Overview of 10AX032E1F29E1HG – Arria 10 GX FPGA, 780‑BBGA FCBGA

The 10AX032E1F29E1HG is an Intel Arria 10 GX field programmable gate array (FPGA) in a 780‑ball FBGA package. It is part of the Arria 10 family of 20 nm mid-range FPGAs and SoCs designed for high‑performance, power‑efficient applications across wireless, wireline, broadcast, computing, medical, and defense markets.

Built for designs that need dense logic, on‑chip RAM, and extensive I/O, this device combines variable‑precision DSP blocks, embedded memory, and hard IP options (for interfaces such as PCIe and high‑speed Ethernet) to accelerate system integration and reduce board-level complexity.

Key Features

- Logic Capacity — 320,000 logic elements to implement complex digital functions and custom accelerators.

- On‑Chip Memory — 21,040,128 total RAM bits of embedded memory for buffering, lookup tables, and state storage.

- I/O Density — 360 I/Os to support a wide range of external interfaces and parallel connectivity.

- Hard IP and Transceivers — Family documentation highlights PCIe Gen1/Gen2/Gen3 hard IP, enhanced PCS for Interlaken and 10 Gbps Ethernet, and low‑power serial transceivers to support high‑speed link implementations.

- DSP and Signal Processing — Variable‑precision DSP blocks for efficient implementation of math‑intensive functions and signal processing pipelines.

- Configuration and Reconfiguration — Supports dynamic and partial reconfiguration capabilities for in‑field updates and flexible system partitioning, as described in family documentation.

- Power and Clocking — On‑chip power management and multiple clocking networks including fractional synthesis and I/O PLLs for precise timing control, per family overview.

- Package and Mounting — 780‑FBGA (29 × 29 mm) package, surface mount, with a 780‑BBGA, FCBGA package case.

- Electrical and Environmental — Voltage supply range 870 mV to 980 mV; operating temperature 0 °C to 100 °C; RoHS compliant; device grade: Extended.

Typical Applications

- Wireless Infrastructure — Channel and switch cards, remote radio head interfaces, and mobile backhaul designs leveraging DSP blocks and high I/O density.

- Wireline and Optical Systems — 40G/100G muxponder and transponder line cards, aggregation and bridging functions using hard IP for high‑speed serial links.

- Broadcast and Professional AV — Studio switches and video transport where large on‑chip memory and flexible I/O facilitate frame buffering and format handling.

- Computing and Storage — Server acceleration, flash cache controllers, and cloud compute offload where logic density and PCIe hard IP aid system integration.

Unique Advantages

- High Logic Density: 320,000 logic elements allow consolidation of multiple functions into a single FPGA, reducing board BOM and interconnect complexity.

- Substantial On‑Chip Memory: Over 21 million bits of embedded RAM support deep buffering and table storage without external memory for many use cases.

- Extensive I/O and High‑Speed Support: 360 I/Os and family‑level support for PCIe and 10 Gbps Ethernet hard IP simplify integration of peripheral and network interfaces.

- Flexible DSP Capability: Variable‑precision DSP blocks enable efficient implementation of diverse signal processing algorithms with optimized resource use.

- Reconfiguration and Power Control: Dynamic and partial reconfiguration plus power management features in the Arria 10 family allow optimization of runtime behavior and power usage.

- Production‑Ready Packaging: 780‑FBGA (29 × 29 mm) surface‑mount package and Extended grade operating range provide a production‑friendly form factor and environmental tolerance.

Why Choose 10AX032E1F29E1HG?

The 10AX032E1F29E1HG Arria 10 GX FPGA targets mid‑range designs that demand a balance of performance, integration, and power efficiency. With 320,000 logic elements, abundant embedded RAM, and extensive I/O, it supports complex data‑processing, networking, and acceleration tasks while leveraging Arria 10 family features such as DSP blocks, hard IP for high‑speed interfaces, and advanced clocking and power management.

This device is suited to engineering teams implementing scalable, reconfigurable systems across wireless, wireline, broadcast, and computing markets that require verified FPGA family capabilities and production‑grade packaging with RoHS compliance and Extended temperature grading.

Request a quote or contact sales to discuss pricing, availability, and lead times for the 10AX032E1F29E1HG.

Date Founded: 1968

Headquarters: Santa Clara, California, USA

Employees: 130,000+

Revenue: $54.23 Billion

Certifications and Memberships: ISO9001:2015, ISO14001:2015, ISO17025:2017, ISO27001:2022, ISO45001:2018, ISO50001:2018