1SD280PT2F55E2VG

| Part Description |

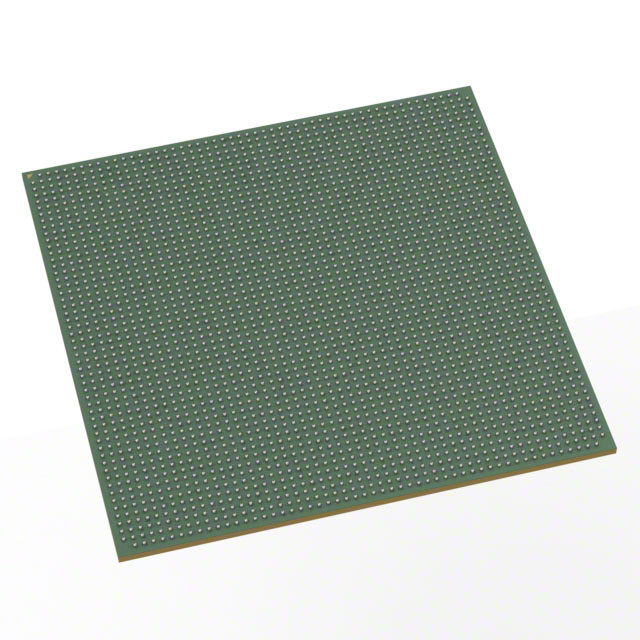

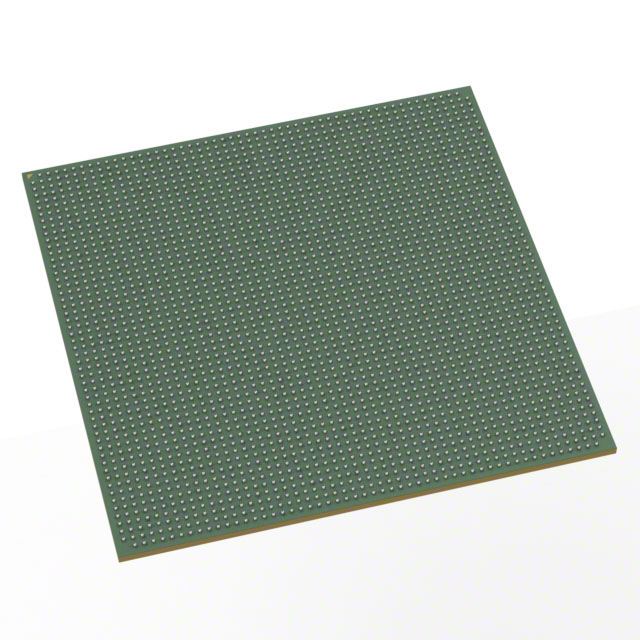

Stratix® 10 DX Field Programmable Gate Array (FPGA) IC 816 240123904 2753000 2912-BBGA, FCBGA |

|---|---|

| Quantity | 1,412 Available (as of May 5, 2026) |

| Product Category | Field Programmable Gate Array (FPGA) |

|---|---|

| Manufacturer | Intel |

| Manufacturing Status | Active |

| Manufacturer Standard Lead Time | 12 Weeks |

| Datasheet |

Specifications & Environmental

| Device Package | 2912-FBGA (55x55) | Grade | Extended | Operating Temperature | 0°C – 100°C | ||

|---|---|---|---|---|---|---|---|

| Package / Case | 2912-BBGA, FCBGA | Number of I/O | 816 | Voltage | 870 mV - 970 mV | ||

| Mounting Method | Surface Mount | RoHS Compliance | Unknown | REACH Compliance | REACH Unaffected | ||

| Moisture Sensitivity Level | 3 (168 Hours) | Number of LABs/CLBs | N/A | Number of Logic Elements/Cells | 2753000 | ||

| Number of Gates | N/A | ECCN | N/A | HTS Code | N/A | ||

| Qualification | N/A | Total RAM Bits | 240123904 |

Overview of 1SD280PT2F55E2VG – Stratix® 10 DX FPGA, 2912-BBGA (55×55), 816 I/O

The 1SD280PT2F55E2VG is a Stratix® 10 DX field programmable gate array (FPGA) designed for high-performance acceleration and advanced I/O integration. As a member of the Stratix 10 DX family, it combines a high-density FPGA fabric with hard intellectual‑property blocks and advanced packaging to address datacenter, networking, cloud computing, and test & measurement applications.

This device delivers large logic and memory resources, extensive I/O, and package-level integration to support coherent and non‑coherent interfaces and demanding system-level designs where performance and integration matter.

Key Features

- High Logic Density — 2,753,000 logic elements (cells) to support large, complex designs and high-throughput algorithms.

- Large Embedded Memory — 240,123,904 total RAM bits for on-chip buffering, state storage, and memory‑intensive processing.

- Extensive I/O — 816 I/O pins to enable wide data buses, multi‑link interfaces, and rich connectivity options.

- Advanced Fabric and Hard IP (Series-Level) — Stratix 10 DX family features the Intel Hyperflex core architecture, hard IP blocks for coherent and non‑coherent protocols, and options such as hard PCIe Gen4 and 100 Gigabit Ethernet IP (series-level capabilities described in the device overview).

- High‑Performance Transceivers (Series-Level) — Heterogeneous transceiver tiles in the Stratix 10 DX family support high-speed serial links for chip‑to‑chip and backplane applications (series-level feature).

- Package and Mounting — 2912‑BBGA FCBGA package (2912‑FBGA, 55×55) with surface mount mounting for dense board integration.

- Power and Operating Range — Core voltage supply range 870 mV to 970 mV; operating temperature range 0 °C to 100 °C; Extended grade device.

- Compliance — RoHS compliant.

Typical Applications

- Datacenter Acceleration — Hardware acceleration for compute workloads where high logic density and large on‑chip memory enable complex algorithms and low-latency processing.

- Networking & Telecom — High-speed serial transceivers and extensive I/O support packet processing, line cards, and optical networking functions (series-level transceiver and IP capabilities).

- Cloud Computing & Storage — Offload and acceleration of storage and memory‑centric tasks using the device’s large RAM resources and interface IP (series-level memory/IP features).

- Test & Measurement — High channel counts and flexible I/O for data acquisition, signal processing, and protocol test systems.

Unique Advantages

- Massive on‑chip resources: 2.75M logic elements and 240M RAM bits provide capacity for large, feature-rich FPGA designs without relying solely on external memory.

- Broad connectivity: 816 I/O pins enable multiport designs and extensive peripheral interfacing for system integration.

- Package integration: 2912‑BBGA FCBGA (55×55) packaging supports high pin count and dense board layouts for space-constrained, high-performance systems.

- Series-level system IP: Stratix 10 DX family features such as hard PCIe Gen4 IP, coherent and non‑coherent protocol support, and advanced transceiver tiles help reduce design risk when those features are required (series-level capabilities).

- Designed for demanding environments: Extended grade rating with 0 °C to 100 °C operating range and RoHS compliance for broad deployment scenarios.

Why Choose 1SD280PT2F55E2VG?

The 1SD280PT2F55E2VG positions itself for system designs that need high logic density, substantial on‑chip memory, and wide I/O in a single, surface‑mount FPGA package. Its specification set supports complex acceleration, networking, and test applications where integration and scalability are key.

For teams targeting datacenter, networking, cloud, or measurement systems, this Stratix 10 DX device delivers the resources and package-level integration to build robust, high-performance solutions while leveraging the family-level IP and architecture described in the device overview.

Request a quote or submit an inquiry to receive pricing and availability information for the 1SD280PT2F55E2VG.

Date Founded: 1968

Headquarters: Santa Clara, California, USA

Employees: 130,000+

Revenue: $54.23 Billion

Certifications and Memberships: ISO9001:2015, ISO14001:2015, ISO17025:2017, ISO27001:2022, ISO45001:2018, ISO50001:2018