1SG110HN1F43E1VG

| Part Description |

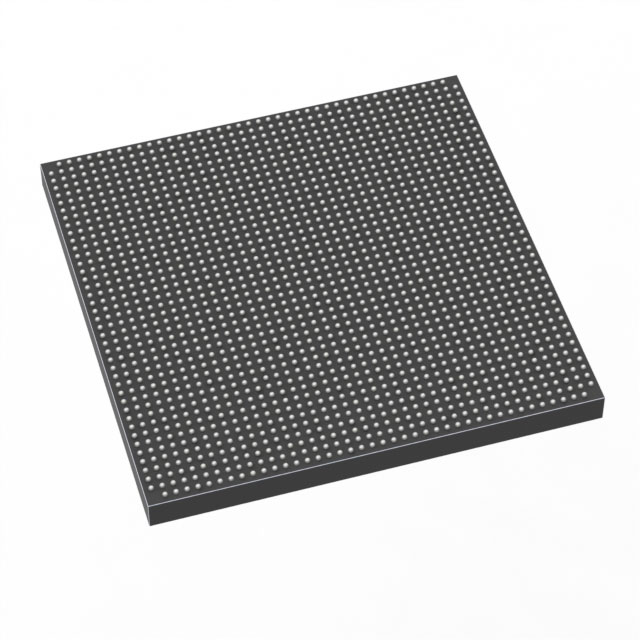

Stratix® 10 GX Field Programmable Gate Array (FPGA) IC 688 1100000 1760-BBGA, FCBGA |

|---|---|

| Quantity | 1,103 Available (as of May 5, 2026) |

| Product Category | Field Programmable Gate Array (FPGA) |

|---|---|

| Manufacturer | Intel |

| Manufacturing Status | Active |

| Manufacturer Standard Lead Time | 8 Weeks |

| Datasheet |

Specifications & Environmental

| Device Package | 1760-FBGA (42.5x42.5) | Grade | Extended | Operating Temperature | 0°C – 100°C | ||

|---|---|---|---|---|---|---|---|

| Package / Case | 1760-BBGA, FCBGA | Number of I/O | 688 | Voltage | 770 mV - 970 mV | ||

| Mounting Method | Surface Mount | RoHS Compliance | Unknown | REACH Compliance | REACH Unaffected | ||

| Moisture Sensitivity Level | 3 (168 Hours) | Number of LABs/CLBs | 137500 | Number of Logic Elements/Cells | 1100000 | ||

| Number of Gates | N/A | ECCN | N/A | HTS Code | N/A | ||

| Qualification | N/A | Total RAM Bits | 112197632 |

Overview of 1SG110HN1F43E1VG – Stratix® 10 GX FPGA IC, 688 I/O, 1760-FBGA

The 1SG110HN1F43E1VG is an Intel Stratix® 10 GX field-programmable gate array (FPGA) supplied in a 1760‑FBGA (42.5 × 42.5 mm) package. It targets high-performance, bandwidth‑intensive applications that require large programmable logic capacity, significant on‑chip memory, and a high I/O count.

Built on the Stratix 10 family architecture, this device combines advanced core architecture and high integration to deliver a platform for demanding communications, data‑center, and compute‑accelerator designs.

Key Features

- Core architecture Stratix® 10 GX family core with Intel Hyperflex™ architecture and Intel 14 nm tri‑gate (FinFET) technology as described for the device family.

- Logic capacity 1,100,000 logic elements, providing large programmable fabric for complex custom logic and algorithms.

- Embedded memory 112,197,632 total RAM bits of on‑chip memory to support large buffering and state storage requirements.

- DSP and compute Variable‑precision DSP blocks and family capabilities described in the Stratix 10 overview (including floating‑point and fixed‑point DSP support) to accelerate signal processing workloads.

- High‑speed transceivers & IP Family features include heterogeneous 3D SiP transceiver tiles, multi‑Gbps transceiver channels, and hard IP such as PCI Express Gen1/Gen2/Gen3 and 10G Ethernet hard IP (as described for the Stratix 10 GX/SX family).

- I/O and package 688 I/O pins in a 1760‑FBGA (42.5 × 42.5 mm) surface‑mount package for dense external connectivity and system integration.

- Power and supply Supported core voltage supply range of 770 mV to 970 mV for the device core domain.

- Operating range and grade Extended grade with an operating temperature range of 0 °C to 100 °C.

- Configuration and reliability features Family documentation describes device configuration, secure device manager (SDM), and SEU detection/correction mechanisms available in the Stratix 10 devices.

- Packaging and mounting Surface‑mount 1760‑BBGA, FCBGA package (supplier device package: 1760‑FBGA, 42.5 × 42.5 mm) for board‑level integration.

Typical Applications

- High‑performance networking Used for line cards, backplane interfaces, and packet processing where large logic capacity, high‑speed transceivers, and embedded memory are required.

- Data‑center acceleration Suitable for custom compute acceleration, offload engines, and data‑path processing needing dense logic and substantial on‑chip RAM.

- High‑speed I/O systems Ideal for systems requiring many external interfaces and high I/O pin counts, including multi‑lane SERDES and PHY integration via available hard IP.

- Signal processing and DSP Applies to advanced signal processing, filtering, and mixed fixed/floating point algorithms leveraging variable‑precision DSP blocks.

Unique Advantages

- High logic density: 1,100,000 logic elements enable implementation of large, complex designs without immediate partitioning across multiple devices.

- Large embedded memory: Over 112 million RAM bits support deep buffering, large lookup tables, and memory‑intensive functions on‑chip.

- Extensive I/O: 688 I/O pins in a 1760‑FBGA package allow high connectivity and flexible board‑level interfacing.

- Family‑level high‑speed connectivity: Stratix 10 family transceiver and hard IP capabilities (including PCIe Gen1/2/3 and 10G Ethernet hard IP) provide pathways to high bandwidth system designs.

- Optimized silicon technology: Built on Intel 14 nm tri‑gate technology with the Hyperflex architecture to deliver improved core performance and efficiency as described for the family.

- Extended operating grade: Rated for 0 °C to 100 °C operation to match many commercial and enterprise deployment environments.

Why Choose 1SG110HN1F43E1VG?

The 1SG110HN1F43E1VG brings Stratix 10 GX family innovations—high logic capacity, substantial embedded memory, a large I/O footprint, and family‑level high‑speed transceiver and IP capabilities—into a single 1760‑FBGA device. It is positioned for engineers building bandwidth‑ and compute‑intensive systems who need a highly programmable platform with strong on‑chip resources.

For designs that require scalability and documented family features such as advanced core architecture, hard IP for high‑speed interfaces, and extensive memory resources, this device provides a compact, integrated option supported by the Stratix 10 device documentation and architecture.

If you would like pricing, availability, or a formal quote for 1SG110HN1F43E1VG, submit a quote request or contact sales to discuss your design requirements and volume needs.

Date Founded: 1968

Headquarters: Santa Clara, California, USA

Employees: 130,000+

Revenue: $54.23 Billion

Certifications and Memberships: ISO9001:2015, ISO14001:2015, ISO17025:2017, ISO27001:2022, ISO45001:2018, ISO50001:2018