1SG280HN3F43E2VG

| Part Description |

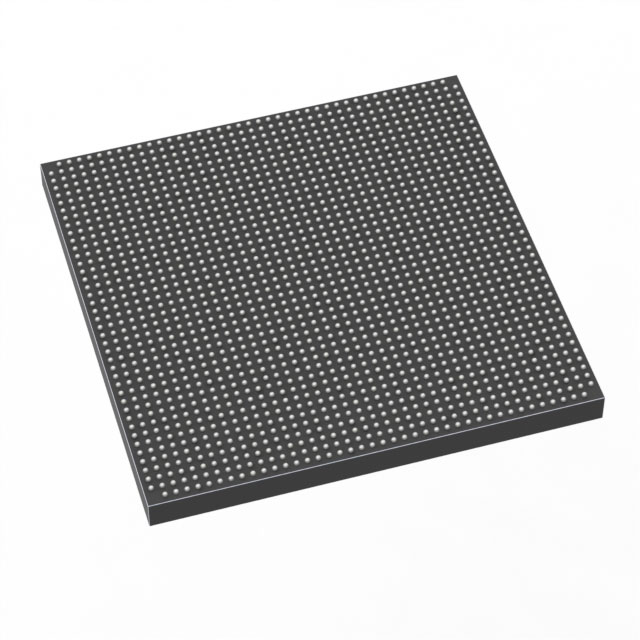

Stratix® 10 GX Field Programmable Gate Array (FPGA) IC 688 2800000 1760-BBGA, FCBGA |

|---|---|

| Quantity | 413 Available (as of May 5, 2026) |

| Product Category | Field Programmable Gate Array (FPGA) |

|---|---|

| Manufacturer | Intel |

| Manufacturing Status | Active |

| Manufacturer Standard Lead Time | 12 Weeks |

| Datasheet |

Specifications & Environmental

| Device Package | 1760-FBGA (42.5x42.5) | Grade | Extended | Operating Temperature | 0°C – 100°C | ||

|---|---|---|---|---|---|---|---|

| Package / Case | 1760-BBGA, FCBGA | Number of I/O | 688 | Voltage | 770 mV - 970 mV | ||

| Mounting Method | Surface Mount | RoHS Compliance | Unknown | REACH Compliance | REACH Unaffected | ||

| Moisture Sensitivity Level | 3 (168 Hours) | Number of LABs/CLBs | 350000 | Number of Logic Elements/Cells | 2800000 | ||

| Number of Gates | N/A | ECCN | N/A | HTS Code | N/A | ||

| Qualification | N/A | Total RAM Bits | 240123904 |

Overview of 1SG280HN3F43E2VG – Stratix® 10 GX Field Programmable Gate Array (FPGA), 1760-BBGA, 688 I/Os

The 1SG280HN3F43E2VG is a Stratix® 10 GX FPGA device designed for high-performance, bandwidth‑intensive applications. As a member of the Stratix 10 GX family, it leverages the Intel Hyperflex™ core architecture and Intel 14 nm tri‑gate (FinFET) technology described for the family to deliver elevated core performance and power efficiency.

With 2,800,000 logic elements, 240,123,904 total RAM bits and 688 user I/Os in a 1760‑BBGA (FCBGA) package, this device targets advanced networking, compute acceleration, and system‑level integration use cases where dense logic, large embedded memory, and high I/O counts are required.

Key Features

- Core Architecture Intel Hyperflex™ core architecture (Stratix 10 family) providing significantly increased core performance versus prior-generation high-performance FPGAs.

- Logic Density 2,800,000 logic elements to implement complex custom logic, protocol stacks and wide data‑path processing.

- Embedded Memory 240,123,904 total RAM bits for large on‑chip buffering, packet staging and scratchpad storage.

- I/O and Package 688 user I/Os in a 1760‑BBGA (FCBGA) package; supplier device package specified as 1760‑FBGA (42.5 × 42.5 mm) for dense board integration.

- Power and Thermal Operating core supply range 770 mV to 970 mV and an operating temperature range of 0 °C to 100 °C; device graded as Extended.

- High‑Speed Interfaces (Family Capabilities) Stratix 10 family documentation describes heterogeneous transceiver tiles, high‑speed serial performance and hard IP such as PCI Express and 10G/40G Ethernet—enabling high‑bandwidth interconnects when implemented in designs.

- System Features (Family Capabilities) Family overview highlights integrated features including programmable PLLs, variable‑precision DSP blocks and hard memory controllers that support high‑speed external DRAM interfaces.

- Manufacturing and Compliance Surface‑mount device; RoHS compliant.

Typical Applications

- Telecommunications & Data Center Networking High logic density, large embedded RAM and family transceiver/IP capabilities make the device suitable for packet processing, switch fabric and line‑card applications that require high I/O and throughput.

- Compute Acceleration Large logic and memory resources support custom acceleration of signal processing, encryption, and data‑plane workloads where FPGA‑based offload is required.

- Storage & High‑Speed IO Hard memory controllers and wide I/O capacity (family features) support high‑performance storage controllers and protocol offloads for enterprise storage systems.

- System Integration & Prototyping Dense logic and extensive on‑chip memory enable complex system prototypes and consolidation of multiple functions into a single FPGA package.

Unique Advantages

- High Logic Capacity: 2,800,000 logic elements provide headroom for large, complex designs and multiple instantiated IP blocks.

- Substantial On‑Chip Memory: 240,123,904 total RAM bits reduce reliance on external memory for buffering and state storage, simplifying system architecture.

- Large I/O Count in a Compact Package: 688 user I/Os in a 1760‑BBGA package support dense board-level connectivity while keeping footprint compact.

- Family-Level High-Speed Capabilities: Stratix 10 family features such as high-speed transceivers, hard PCIe and Ethernet IP enable designers to implement high-bandwidth interfaces and protocol offloads.

- Designed for System-Level Performance: Hyperflex core architecture and 14 nm tri‑gate technology (family attributes) tie into improved performance-per-watt for compute- and bandwidth‑heavy tasks.

- Compliance and Assembly: Surface‑mount form factor and RoHS compliance ease manufacturing and regulatory integration into commercial systems.

Why Choose 1SG280HN3F43E2VG?

The 1SG280HN3F43E2VG delivers a compelling combination of dense logic, large on‑chip memory and high I/O capacity in a single Stratix 10 GX FPGA package. It is positioned for designers building demanding networking, compute acceleration and storage applications that require substantial programmable resources together with family‑level high‑speed interface capabilities.

Choosing this device supports scalable, system‑level designs that leverage the Stratix 10 family innovations documented in the device overview—allowing engineering teams to consolidate functions, reduce board complexity and pursue high‑throughput architectures with a proven FPGA silicon family.

Request a quote or submit an inquiry to receive pricing, availability and technical assistance for 1SG280HN3F43E2VG.

Date Founded: 1968

Headquarters: Santa Clara, California, USA

Employees: 130,000+

Revenue: $54.23 Billion

Certifications and Memberships: ISO9001:2015, ISO14001:2015, ISO17025:2017, ISO27001:2022, ISO45001:2018, ISO50001:2018