1SG280HU2F50E2VG

| Part Description |

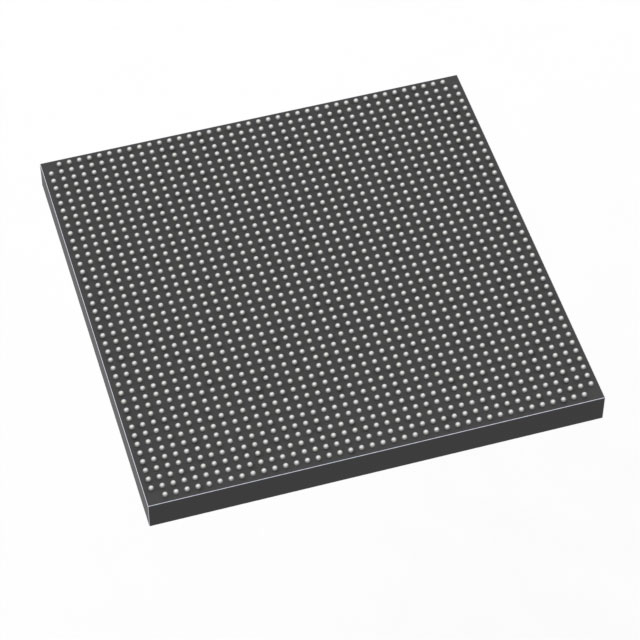

Stratix® 10 GX Field Programmable Gate Array (FPGA) IC 704 2800000 2397-BBGA, FCBGA |

|---|---|

| Quantity | 1,492 Available (as of May 5, 2026) |

| Product Category | Field Programmable Gate Array (FPGA) |

|---|---|

| Manufacturer | Intel |

| Manufacturing Status | Active |

| Manufacturer Standard Lead Time | 12 Weeks |

| Datasheet |

Specifications & Environmental

| Device Package | 2397-FBGA, FC (50x50) | Grade | Extended | Operating Temperature | 0°C – 100°C | ||

|---|---|---|---|---|---|---|---|

| Package / Case | 2397-BBGA, FCBGA | Number of I/O | 704 | Voltage | 770 mV - 970 mV | ||

| Mounting Method | Surface Mount | RoHS Compliance | Unknown | REACH Compliance | REACH Unaffected | ||

| Moisture Sensitivity Level | 3 (168 Hours) | Number of LABs/CLBs | 350000 | Number of Logic Elements/Cells | 2800000 | ||

| Number of Gates | N/A | ECCN | N/A | HTS Code | N/A | ||

| Qualification | N/A | Total RAM Bits | 240123904 |

Overview of 1SG280HU2F50E2VG – Stratix® 10 GX FPGA, 704 I/O, 2397-BBGA (FCBGA)

The 1SG280HU2F50E2VG is an Intel Stratix® 10 GX field programmable gate array (FPGA) in a 2397-BBGA FCBGA package. It delivers large programmable logic capacity and extensive on-chip memory, targeting advanced applications that require high bandwidth, heavy processing and flexible hardware acceleration.

Built on the Stratix 10 GX family innovations, the device leverages the Intel Hyperflex™ core architecture and Intel 14 nm tri-gate (FinFET) process to address demanding communications and compute use cases while providing a high-density I/O footprint.

Key Features

- Core architecture Intel Hyperflex core architecture is a documented family innovation that delivers significantly increased core performance versus previous-generation high-performance FPGAs.

- Logic capacity 2,800,000 logic elements, providing large programmable fabric for complex designs and hardware acceleration.

- On-chip memory 240,123,904 total RAM bits and family‑level M20K internal SRAM memory blocks for large buffering, lookup tables and state storage.

- I/O and transceiver capability 704 I/O pins in a high-density I/O configuration; the Stratix 10 family documentation also highlights heterogeneous 3D SiP transceiver tiles and high-speed transceiver support for demanding serial links.

- Hard IP options (family level) Family documentation includes hard PCI Express Gen3 x16 IP and hardened Ethernet/forward error correction options for common high-speed protocols.

- Process and integration Intel 14 nm tri-gate (FinFET) technology and Hyperflex innovations enable higher performance and power efficiency at the device family level.

- Power supply range Supported core voltage range from 770 mV to 970 mV for core power planning and regulator selection.

- Package and mounting 2397-BBGA, FCBGA package (supplier device package: 2397-FBGA, FC 50×50) with surface mount mounting type for high-density board integration.

- Temperature and grade Extended grade device with an operating temperature range of 0°C to 100°C.

- RoHS compliance Device is RoHS compliant.

Typical Applications

- High‑performance networking Implements packet processing, forwarding, and protocol offload where large logic capacity, on-chip memory and high-density I/O are required.

- Data center acceleration Hardware acceleration for compute and storage tasks that benefit from large FPGA fabric and embedded memory for buffering and stateful operations.

- Telecommunications infrastructure Backplane and line-card designs that require programmable logic for protocol handling, FEC and high-speed serial connectivity.

- Test and measurement systems Real-time signal processing and custom instrumentation using the abundant logic elements and on-chip RAM.

Unique Advantages

- Large programmable capacity: 2.8 million logic elements enable integration of complex algorithms and multiple hardware accelerators on a single device.

- Substantial on-chip memory: 240,123,904 RAM bits reduce external memory dependence for many buffering and stateful workloads.

- High-density I/O: 704 I/O pins in a compact FCBGA package support designs with numerous interfaces and parallel buses.

- Modern process and architecture (family level): 14 nm FinFET process combined with Intel Hyperflex core architecture delivers family-documented performance and efficiency improvements.

- Board-level integration: 2397-BBGA (50×50) packaging and surface-mount mounting enable dense, manufacturable PCB layouts for complex systems.

- Compliance and grade: RoHS compliant and extended grade temperature rating support typical commercial and enterprise deployment environments.

Why Choose 1SG280HU2F50E2VG?

The 1SG280HU2F50E2VG brings substantial logic density, large embedded RAM and a high I/O count in a compact 2397-BBGA FCBGA package. It is positioned for engineers developing advanced networking, compute acceleration and communications infrastructure who need on-board resources to implement complex, high-throughput designs.

Supported by Stratix 10 family architecture and documented innovations, this device offers a scalable platform for designs that require significant on-chip resources, modern process advantages and extensive I/O integration—making it suitable for projects where consolidation of functionality into a single FPGA can simplify system architecture and reduce BOM complexity.

Request a quote or submit an inquiry to learn about availability, lead times and pricing for the 1SG280HU2F50E2VG.

Date Founded: 1968

Headquarters: Santa Clara, California, USA

Employees: 130,000+

Revenue: $54.23 Billion

Certifications and Memberships: ISO9001:2015, ISO14001:2015, ISO17025:2017, ISO27001:2022, ISO45001:2018, ISO50001:2018