1ST085EN3F43E3VGAS

| Part Description |

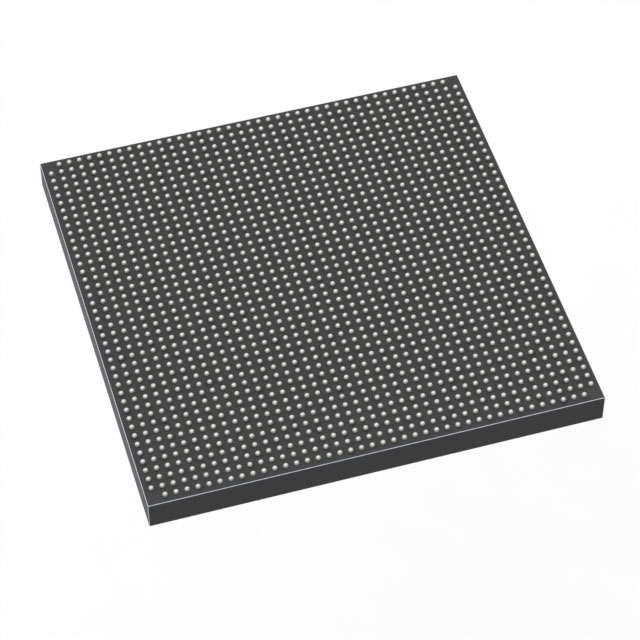

Stratix® 10 TX Field Programmable Gate Array (FPGA) IC 440 850000 1760-BBGA, FCBGA |

|---|---|

| Quantity | 887 Available (as of May 5, 2026) |

| Product Category | Field Programmable Gate Array (FPGA) |

|---|---|

| Manufacturer | Intel |

| Manufacturing Status | Active |

| Manufacturer Standard Lead Time | 12 Weeks |

| Datasheet |

Specifications & Environmental

| Device Package | 1760-FBGA (42.5x42.5) | Grade | Extended | Operating Temperature | 0°C – 100°C | ||

|---|---|---|---|---|---|---|---|

| Package / Case | 1760-BBGA, FCBGA | Number of I/O | 440 | Voltage | 770 mV - 970 mV | ||

| Mounting Method | Surface Mount | RoHS Compliance | Unknown | REACH Compliance | REACH Unaffected | ||

| Moisture Sensitivity Level | 3 (168 Hours) | Number of LABs/CLBs | 106250 | Number of Logic Elements/Cells | 850000 | ||

| Number of Gates | N/A | ECCN | N/A | HTS Code | N/A | ||

| Qualification | N/A | Total RAM Bits | 71303168 |

Overview of 1ST085EN3F43E3VGAS – Stratix® 10 TX FPGA, 440 I/O, 850,000 Logic Elements, 1760‑BBGA

The 1ST085EN3F43E3VGAS is a Stratix® 10 TX field programmable gate array (FPGA) in a 1760‑BBGA (42.5 × 42.5 mm) package, featuring 850,000 logic elements and 440 user I/O. It implements Intel’s HyperFlex® core architecture and is part of the Stratix 10 TX family, which emphasizes high transceiver bandwidth, hardened networking IP, and advanced packaging integration.

Targeted at high‑bandwidth systems, this device combines a large logic fabric with on‑chip RAM (71,303,168 bits total), dual‑mode high‑speed transceiver capabilities at the series level, and hardened protocol IP in the Stratix 10 TX family to address next‑generation networking, data center, and high‑performance compute applications.

Key Features

- Logic Capacity — 850,000 logic elements (LEs) for complex, area‑intensive designs and high gate counts.

- On‑chip Memory — 71,303,168 total RAM bits to support large buffering, lookup tables, and embedded data structures.

- I/O — 440 user I/O pins, enabling wide parallel interfaces and high pin‑count connectivity.

- Transceiver and Series-Level Capabilities — Stratix 10 TX family features dual‑mode transceivers capable of 57.8 Gbps PAM4 and 28.9 Gbps NRZ operation and family‑level hardened 10/25/100 Gbps Ethernet and PCIe Gen3 IP blocks; these series innovations enable multi‑Tbps aggregated bandwidth in system designs.

- Package and Mounting — 1760‑BBGA (FCBGA) supplier package (42.5 × 42.5 mm), surface‑mount package suitable for compact, high‑density boards.

- Power and Supply — Core voltage supply range 770 mV to 970 mV, supporting the device’s power domains and dynamic power architectures.

- Operating Range and Grade — Extended grade with operating temperature specified from 0 °C to 100 °C.

- Compliance — RoHS compliant.

Typical Applications

- High‑Speed Networking & Telecommunications — Leverage the Stratix 10 TX family’s high‑rate transceivers and hardened Ethernet IP to implement backplane, switch, and line‑card functions requiring multi‑Gbps serial links and protocol offload.

- Data Center & High‑Performance Computing — Use the large logic element count and substantial on‑chip RAM for packet processing, acceleration engines, and custom compute pipelines.

- Chip‑to‑Module and Backplane Interfaces — Support chip‑to‑chip and chip‑to‑module links using high‑bandwidth, dual‑mode transceivers at the series level for board‑level and system‑level interconnects.

- Embedded Processing Platforms — For designs that require a hardened processor subsystem (available in select series devices), integrate application‑class processing with FPGA fabric to reduce component count and improve throughput.

Unique Advantages

- High Logic Integration: 850,000 logic elements deliver capacity for complex algorithms, custom accelerators, and wide datapaths without external partitioning.

- Substantial On‑Chip Memory: Over 71 million bits of RAM reduce dependency on external memory for buffering and on‑chip data structures, simplifying memory architecture.

- Series‑Level High‑Speed I/O: Stratix 10 TX family dual‑mode transceiver technology and hardened networking IP provide a clear upgrade path for multi‑Gbps serial link designs.

- Compact, High‑Density Package: 1760‑BBGA FCBGA footprint (42.5 × 42.5 mm) supports dense board layouts while providing abundant I/O and routing resources.

- Power Domain Flexibility: Operates with a core supply range of 770 mV to 970 mV to align with target power budgets and dynamic power management strategies.

- Extended Temperature Grade: Rated for 0 °C to 100 °C operation to match thermal requirements for many server and communications environments.

Why Choose 1ST085EN3F43E3VGAS?

The 1ST085EN3F43E3VGAS combines a high logic element count, large embedded RAM, and extensive I/O in a compact 1760‑BBGA package, making it suitable for demanding networking and compute applications that require significant programmable logic and on‑chip memory. As part of the Stratix 10 TX family, it benefits from the series innovations—HyperFlex core architecture and high‑speed transceiver technology—used to achieve high aggregate bandwidth and hardened protocol support at the family level.

This FPGA is a fit for engineers and system architects building high‑bandwidth switching, data‑plane acceleration, and interface‑intensive platforms who need a high‑capacity, RoHS‑compliant device with extended temperature capability and the package density required for modern system boards.

Request a quote or submit an inquiry to receive pricing and availability information for the 1ST085EN3F43E3VGAS and to discuss how this Stratix 10 TX FPGA can meet your project requirements.

Date Founded: 1968

Headquarters: Santa Clara, California, USA

Employees: 130,000+

Revenue: $54.23 Billion

Certifications and Memberships: ISO9001:2015, ISO14001:2015, ISO17025:2017, ISO27001:2022, ISO45001:2018, ISO50001:2018