1ST165EU3F50E3VG

| Part Description |

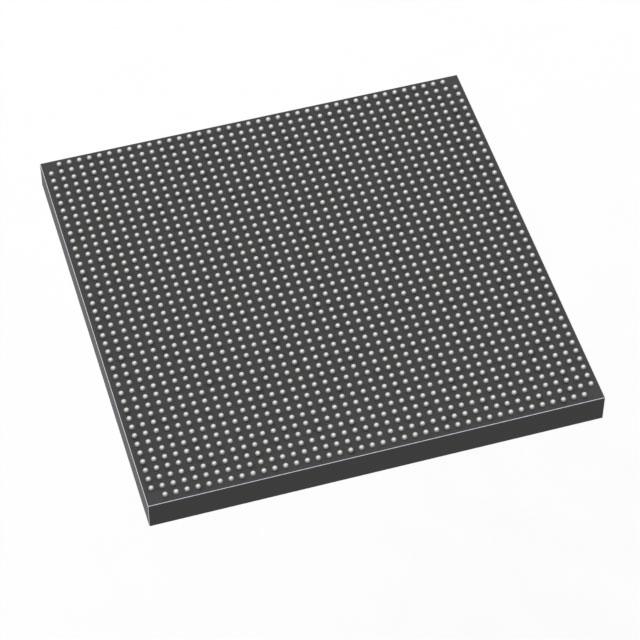

Stratix® 10 TX Field Programmable Gate Array (FPGA) IC 440 1650000 2397-BBGA, FCBGA |

|---|---|

| Quantity | 460 Available (as of May 5, 2026) |

| Product Category | Field Programmable Gate Array (FPGA) |

|---|---|

| Manufacturer | Intel |

| Manufacturing Status | Active |

| Manufacturer Standard Lead Time | 12 Weeks |

| Datasheet |

Specifications & Environmental

| Device Package | 2397-FBGA, FC (50x50) | Grade | Extended | Operating Temperature | 0°C – 100°C | ||

|---|---|---|---|---|---|---|---|

| Package / Case | 2397-BBGA, FCBGA | Number of I/O | 440 | Voltage | 770 mV - 970 mV | ||

| Mounting Method | Surface Mount | RoHS Compliance | Unknown | REACH Compliance | REACH Unaffected | ||

| Moisture Sensitivity Level | 3 (168 Hours) | Number of LABs/CLBs | 206250 | Number of Logic Elements/Cells | 1650000 | ||

| Number of Gates | N/A | ECCN | N/A | HTS Code | N/A | ||

| Qualification | N/A | Total RAM Bits | 119537664 |

Overview of 1ST165EU3F50E3VG – Stratix® 10 TX FPGA, 1,650,000 logic elements

The 1ST165EU3F50E3VG is a Stratix® 10 TX Field Programmable Gate Array (FPGA) IC from Intel, featuring a large monolithic fabric and advanced transceiver capabilities. The device combines the Intel HyperFlex® core architecture with high‑speed dual‑mode transceivers and hardened protocol IP to address high‑bandwidth networking, communication and complex system integration applications.

This part delivers 1,650,000 logic elements, 119,537,664 bits of on‑chip RAM and up to 440 I/O pins in a 2397‑BBGA FCBGA package. It is offered in Extended grade with an operating range of 0 °C to 100 °C and a core voltage supply range of 770 mV to 970 mV.

Key Features

- Core architecture Intel HyperFlex® core architecture is implemented in the Stratix 10 TX family to improve core performance compared to prior generations.

- Logic capacity 1,650,000 logic elements provide large programmable fabric capacity for complex logic and custom system functions.

- High‑speed transceivers Dual‑mode transceivers support both 57.8 Gbps PAM4 and 28.9 Gbps NRZ operation for chip‑to‑chip, chip‑to‑module and backplane links.

- On‑chip memory 119,537,664 total RAM bits of internal memory to support buffers, packet processing and large data structures; family devices also reference embedded eSRAM and M20K memory block architectures.

- Hardened protocol IP Device family includes hardened PCI Express Gen3 and 10/25/100 Gbps Ethernet MAC IP blocks with dedicated FEC capabilities for high‑performance connectivity.

- I/O and package 440 I/O pins in a 2397‑BBGA (FCBGA) package; supplier device package listed as 2397‑FBGA, FC (50×50). Surface‑mount mounting type.

- Power and operating range Core supply range 770 mV to 970 mV; Extended grade operating temperature 0 °C to 100 °C.

- Advanced packaging Series implements heterogeneous 3D SiP transceiver tiles and EMIB packaging techniques to integrate fabric and high‑speed transceivers.

- Reliability and system features Device family documentation references power management, device configuration, secure device manager and SEU error detection and correction features.

- Compliance RoHS compliant.

Typical Applications

- High‑speed networking and switching Use the device for 10/25/100 Gbps Ethernet switching, routing and MAC acceleration that require hardened Ethernet MAC IP and high transceiver bandwidth.

- Telecommunications and optical transport Designed for backplane and module links in telecom equipment where PAM4 and NRZ transceiver modes and FEC are required.

- Data center interconnect Suitable for aggregation, packet processing and interconnect fabrics that need large programmable logic capacity and abundant on‑chip memory.

- Chip‑to‑chip and module interfaces Provides high‑rate SERDES for chip‑to‑chip and chip‑to‑module connectivity in complex multi‑die systems.

Unique Advantages

- High fabric capacity: 1,650,000 logic elements give designers room for large, integrated FPGA designs without immediate partitioning to multiple devices.

- Dual‑mode high‑speed I/O: Transceivers supporting 57.8 Gbps PAM4 and 28.9 Gbps NRZ enable flexible deployment across optical, backplane and module applications.

- Built‑in protocol IP: Hardened PCIe Gen3 and multi‑rate Ethernet MACs reduce soft‑IP integration effort and accelerate time‑to‑market for connectivity functions.

- Substantial on‑chip RAM: 119,537,664 bits of internal RAM support large packet buffers, lookup tables and state storage for high‑throughput designs.

- Advanced packaging and integration: Heterogeneous 3D SiP and EMIB packaging approaches integrate transceiver tiles with the monolithic fabric to simplify high‑bandwidth system design.

- Extended operating grade: Extended grade and a 0 °C to 100 °C operating range meet typical commercial to higher‑temperature system requirements.

Why Choose 1ST165EU3F50E3VG?

The 1ST165EU3F50E3VG combines a large programmable fabric, substantial on‑chip memory and high‑speed dual‑mode transceivers in a single FCBGA package, making it well suited for high‑bandwidth networking, telecom and data center applications that require integrated protocol IP and robust SERDES performance. Its Extended grade, defined core voltage range and surface‑mount package support deployment in demanding system designs.

Backed by the Stratix 10 TX device family architecture and technical documentation, this FPGA is a practical choice for engineers building scalable, high‑performance systems that integrate complex logic, high‑speed I/O and hardened protocol interfaces.

Request a quote or submit an inquiry to discuss availability, lead times and pricing for the 1ST165EU3F50E3VG.

Date Founded: 1968

Headquarters: Santa Clara, California, USA

Employees: 130,000+

Revenue: $54.23 Billion

Certifications and Memberships: ISO9001:2015, ISO14001:2015, ISO17025:2017, ISO27001:2022, ISO45001:2018, ISO50001:2018