1ST210EU1F50E2VG

| Part Description |

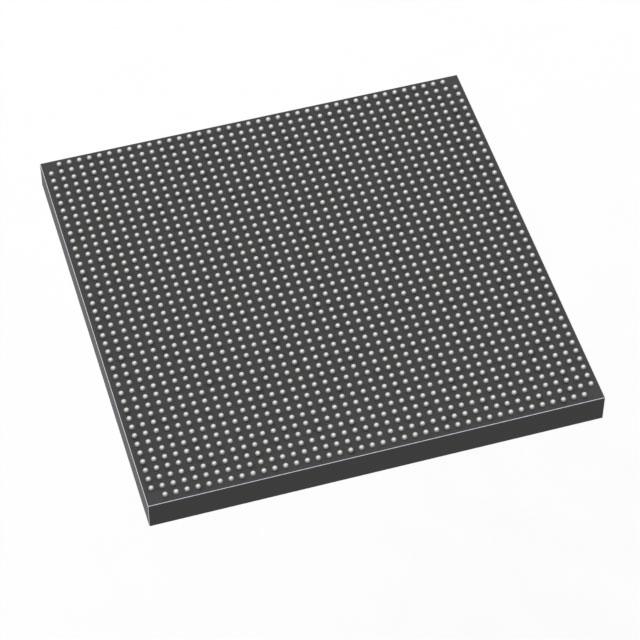

Stratix® 10 TX Field Programmable Gate Array (FPGA) IC 440 2100000 2397-BBGA, FCBGA |

|---|---|

| Quantity | 891 Available (as of May 5, 2026) |

| Product Category | Field Programmable Gate Array (FPGA) |

|---|---|

| Manufacturer | Intel |

| Manufacturing Status | Active |

| Manufacturer Standard Lead Time | 12 Weeks |

| Datasheet |

Specifications & Environmental

| Device Package | 2397-FBGA, FC (50x50) | Grade | Extended | Operating Temperature | 0°C – 100°C | ||

|---|---|---|---|---|---|---|---|

| Package / Case | 2397-BBGA, FCBGA | Number of I/O | 440 | Voltage | 770 mV - 970 mV | ||

| Mounting Method | Surface Mount | RoHS Compliance | Unknown | REACH Compliance | REACH Unaffected | ||

| Moisture Sensitivity Level | 3 (168 Hours) | Number of LABs/CLBs | 262500 | Number of Logic Elements/Cells | 2100000 | ||

| Number of Gates | N/A | ECCN | N/A | HTS Code | N/A | ||

| Qualification | N/A | Total RAM Bits | 133169152 |

Overview of 1ST210EU1F50E2VG – Stratix® 10 TX FPGA, 440 I/Os, 2,100,000 logic elements, 2397‑BBGA

The 1ST210EU1F50E2VG is an Intel Stratix® 10 TX field programmable gate array (FPGA) supplied in a 2397‑BBGA FCBGA package with surface‑mount mounting. It combines a high‑density monolithic FPGA fabric with family‑level innovations such as the Intel Hyperflex core architecture and advanced 14 nm tri‑gate (FinFET) process.

Designed for next‑generation high‑bandwidth designs, the device delivers large logic capacity, extensive on‑chip memory, and integrated high‑speed transceiver and hardened IP capabilities to address demanding datacenter, networking, and high‑performance compute connectivity requirements.

Key Features

- Core & architecture Intel Hyperflex core architecture implemented in 14 nm tri‑gate (FinFET) technology, delivering the family‑level performance improvements documented for Stratix 10 TX devices.

- Logic capacity 2,100,000 logic elements for high‑density logic implementations; family devices can scale to higher logic counts where required.

- On‑chip memory Total RAM capacity of 133,169,152 bits, with internal M20K blocks and select devices offering embedded eSRAM as described in the device family overview.

- High‑speed transceivers & interfaces Family‑level dual‑mode transceivers supporting 57.8 Gbps PAM4 and 28.9 Gbps NRZ operation; hardened IP blocks for PCI Express Gen3 and 10/25/100 Gbps Ethernet are included at the family level.

- DSP & embedded processing Hardened floating‑point DSP blocks are part of the Stratix 10 TX feature set; select devices in the family include an embedded quad‑core 64‑bit Arm Cortex‑A53 hard processor system (HPS).

- I/O & packaging 440 user I/Os in a 2397‑BBGA FCBGA package (supplier package 2397‑FBGA FC, 50×50 mm), surface‑mount mounting.

- Power & operating range Core voltage supply range 770 mV to 970 mV; operating temperature 0 °C to 100 °C; device grade: Extended.

- Standards & compliance RoHS compliant.

Typical Applications

- High‑bandwidth networking Use the device where multi‑lane 10/25/100 Gbps Ethernet and high‑speed PAM4/NRZ transceiver capability are required for switch, router, or line card designs.

- Data center and acceleration Implement custom acceleration and offload functions using the large logic array, abundant on‑chip RAM, and hardened PCIe Gen3 IP blocks (family‑level feature).

- Backplane and chip‑to‑chip connectivity Leverage dual‑mode transceivers for backplane, board‑to‑board, and chip‑to‑chip links at high aggregate bandwidth.

- DSP and signal processing Deploy the device for high‑precision signal processing using the hardened floating‑point DSP resources and extensive logic fabric.

Unique Advantages

- High logic density: 2,100,000 logic elements enable complex, large‑scale designs without partitioning across multiple FPGAs.

- Integrated high‑speed I/O: Dual‑mode transceivers and family‑level hardened Ethernet and PCIe IP simplify high‑bandwidth interface design and reduce external component count.

- Substantial on‑chip memory: 133,169,152 bits of RAM support large buffering, packet processing, and stateful algorithms on‑chip.

- Robust packaging: 2397‑BBGA FCBGA with 440 I/Os and surface‑mount mounting provides a compact, high‑pin‑count solution for dense board layouts.

- Operational range and compliance: Extended grade with 0 °C to 100 °C operating range, RoHS compliance, and defined core voltage range for predictable system design.

Why Choose 1ST210EU1F50E2VG?

The 1ST210EU1F50E2VG places large logic capacity, comprehensive memory resources, and Stratix 10 TX family innovations into a single, high‑pin‑count package. It is positioned for engineers building high‑bandwidth, compute‑intensive systems that require integrated transceiver performance and hardened interface IP described in the Stratix 10 TX device overview.

For designs that need scalability in logic and I/O, combined with family‑level architectural advantages such as the Hyperflex core and FinFET process, this device offers a consolidated platform that reduces external components while delivering the documented capabilities of the Stratix 10 TX family.

Request a quote or submit an inquiry to get pricing and availability for the 1ST210EU1F50E2VG. Our team can provide lead‑time and supply details to support your project planning.

Date Founded: 1968

Headquarters: Santa Clara, California, USA

Employees: 130,000+

Revenue: $54.23 Billion

Certifications and Memberships: ISO9001:2015, ISO14001:2015, ISO17025:2017, ISO27001:2022, ISO45001:2018, ISO50001:2018