1ST210EU2F50I2LGAS

| Part Description |

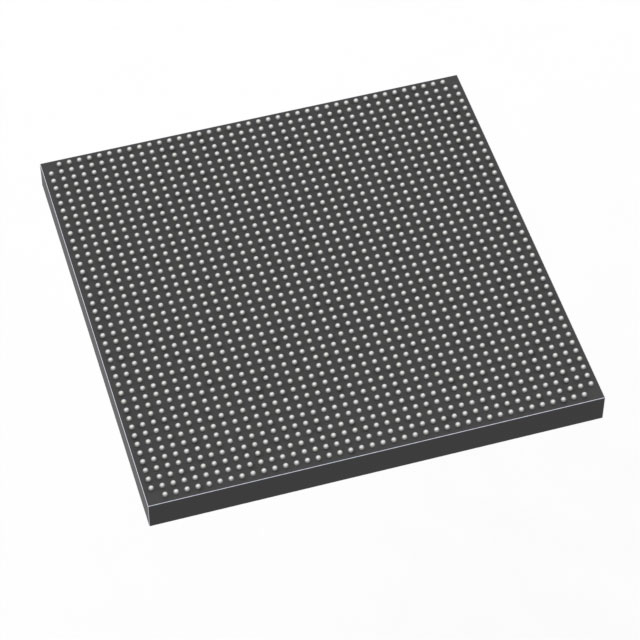

Stratix® 10 TX Field Programmable Gate Array (FPGA) IC 440 2100000 2397-BBGA, FCBGA |

|---|---|

| Quantity | 382 Available (as of May 5, 2026) |

| Product Category | Field Programmable Gate Array (FPGA) |

|---|---|

| Manufacturer | Intel |

| Manufacturing Status | Active |

| Manufacturer Standard Lead Time | 8 Weeks |

| Datasheet |

Specifications & Environmental

| Device Package | 2397-FBGA, FC (50x50) | Grade | Industrial | Operating Temperature | -40°C – 100°C | ||

|---|---|---|---|---|---|---|---|

| Package / Case | 2397-BBGA, FCBGA | Number of I/O | 440 | Voltage | 820 mV - 880 mV | ||

| Mounting Method | Surface Mount | RoHS Compliance | Unknown | REACH Compliance | REACH Unaffected | ||

| Moisture Sensitivity Level | 3 (168 Hours) | Number of LABs/CLBs | 262500 | Number of Logic Elements/Cells | 2100000 | ||

| Number of Gates | N/A | ECCN | N/A | HTS Code | N/A | ||

| Qualification | N/A | Total RAM Bits | 133169152 |

Overview of 1ST210EU2F50I2LGAS – Stratix® 10 TX FPGA, 2,100,000 Logic Elements, 440 I/O, 2397-BBGA

The 1ST210EU2F50I2LGAS is an Intel Stratix® 10 TX field programmable gate array (FPGA) implementing the HyperFlex® core architecture on a 14 nm FinFET fabric. It delivers a very high logic capacity and extensive on-chip RAM, combined with high-speed transceiver capability and hardened protocol IP suitable for demanding communications, networking, and compute-accelerated designs.

Designed for industrial-grade applications, this device integrates 2,100,000 logic elements, 133,169,152 total RAM bits, and up to 440 general-purpose I/O in a 2397‑BBGA (FCBGA) package, and supports low-voltage core operation and wide operating temperature for robust system deployment.

Key Features

- Core and Architecture HyperFlex® core architecture implemented on Intel 14 nm FinFET technology, delivering high-performance FPGA fabric for complex logic and compute functions.

- Logic Capacity 2,100,000 logic elements for large-scale logic integration and high-density designs.

- On-Chip Memory 133,169,152 total RAM bits (internal embedded memory and M20K blocks referenced in the device family) to support buffering, large state machines, and memory-intensive algorithms.

- High-Speed Transceivers Family-level transceiver capability includes dual-mode operation up to 57.8 Gbps PAM4 and 28.9 Gbps NRZ, enabling high-bandwidth chip-to-chip, module, and backplane links.

- Hardened Protocol IP Device family includes hardened PCI Express Gen3 and Ethernet MAC IP blocks (10/25/100 Gbps with dedicated FEC in family documentation) for reduced soft‑IP implementation effort.

- I/O and Package 440 general-purpose I/O in a 2397‑BBGA (FCBGA) package; supplier device package noted as 2397‑FBGA, FC (50×50).

- Power and Voltage Core voltage supply range specified at 820 mV to 880 mV to match low-voltage FPGA core requirements.

- Industrial Temperature Range Rated operating temperature from −40 °C to 100 °C for deployment in industrial environments.

- Security and Configuration (Family Level) Device family documentation references secure device manager (SDM) and configuration features, applicable to system security and provisioning workflows.

Typical Applications

- High‑Bandwidth Networking Used in switches, routers, and line cards where multi‑terabit aggregate bandwidth and hardened Ethernet MACs with FEC accelerate packet processing and link reliability.

- Data Center & Compute Acceleration Deployable for hardware acceleration of data‑intensive workloads that require large logic capacity and significant on‑chip memory for buffering and streaming.

- Telecom Backplane and Optical Modules Supports chip‑to‑chip and backplane interconnects with dual‑mode transceivers (PAM4/NRZ) and high channel counts for modern transport networks.

- High‑Performance Embedded Systems Ideal for systems that demand dense programmable logic, extensive I/O, and industrial temperature operation for ruggedized applications.

Unique Advantages

- Very High Logic Density: 2,100,000 logic elements enable consolidation of complex functions and reduce the need for multiple devices on a board.

- Large On‑Chip Memory: 133,169,152 RAM bits support deep buffering and high‑throughput data paths without immediate reliance on external memory.

- Advanced Transceiver Capability: Family‑level dual‑mode transceivers up to 57.8 Gbps PAM4/28.9 Gbps NRZ provide flexibility for next‑generation link architectures.

- Industrial‑Grade Operation: −40 °C to 100 °C operating range and surface‑mount package options facilitate deployment in industrial environments.

- Hardened Protocol Support: Inclusion of hardened PCIe Gen3 and Ethernet MAC IP at the family level reduces integration time for standard high‑speed interfaces.

- Compact, High‑Density Package: 2397‑BBGA (FCBGA) package offers significant I/O and die integration in a compact form factor for space‑constrained boards.

Why Choose 1ST210EU2F50I2LGAS?

The 1ST210EU2F50I2LGAS brings a combination of high logic capacity, substantial on‑chip memory, and advanced transceiver and hardened IP capabilities from the Stratix® 10 TX family, packaged for industrial temperature operation. These attributes make it suitable for designs that require scalable programmable logic, high aggregate bandwidth, and durable operation in demanding environments.

For engineering teams targeting networking, telecom, compute acceleration, or other high‑performance embedded applications, this device provides a platform to consolidate functions, reduce board-level complexity, and leverage family-level features such as HyperFlex® architecture and hardened protocol IP to accelerate time to market.

If you would like a quote or further technical pricing information for 1ST210EU2F50I2LGAS, submit a request for a quote or contact our sales channel to get product availability and purchasing details.

Date Founded: 1968

Headquarters: Santa Clara, California, USA

Employees: 130,000+

Revenue: $54.23 Billion

Certifications and Memberships: ISO9001:2015, ISO14001:2015, ISO17025:2017, ISO27001:2022, ISO45001:2018, ISO50001:2018