1ST250EU2F50E2VG

| Part Description |

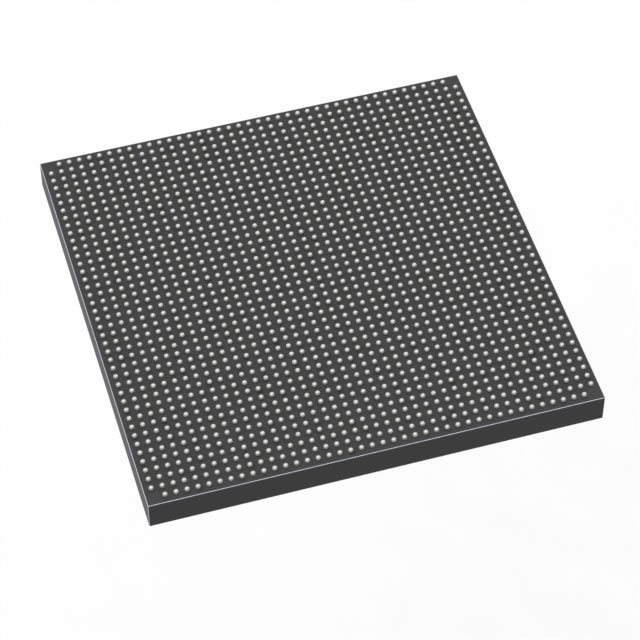

Stratix® 10 TX Field Programmable Gate Array (FPGA) IC 440 2500000 2397-BBGA, FCBGA |

|---|---|

| Quantity | 787 Available (as of May 5, 2026) |

| Product Category | Field Programmable Gate Array (FPGA) |

|---|---|

| Manufacturer | Intel |

| Manufacturing Status | Active |

| Manufacturer Standard Lead Time | 12 Weeks |

| Datasheet |

Specifications & Environmental

| Device Package | 2397-FBGA, FC (50x50) | Grade | Extended | Operating Temperature | 0°C – 100°C | ||

|---|---|---|---|---|---|---|---|

| Package / Case | 2397-BBGA, FCBGA | Number of I/O | 440 | Voltage | 770 mV - 970 mV | ||

| Mounting Method | Surface Mount | RoHS Compliance | Unknown | REACH Compliance | REACH Unaffected | ||

| Moisture Sensitivity Level | 3 (168 Hours) | Number of LABs/CLBs | 312500 | Number of Logic Elements/Cells | 2500000 | ||

| Number of Gates | N/A | ECCN | N/A | HTS Code | N/A | ||

| Qualification | N/A | Total RAM Bits | 204472320 |

Overview of 1ST250EU2F50E2VG – Stratix® 10 TX FPGA, 2,500,000 logic elements, 440 I/O, 2397-BBGA FCBGA

The 1ST250EU2F50E2VG is a Stratix® 10 TX Field Programmable Gate Array (FPGA) in a 2397-BBGA FCBGA package. It delivers a large programmable fabric with 2,500,000 logic elements and a high I/O count for complex, high-throughput system designs.

As part of the Stratix 10 TX family, this device is designed for high-bandwidth applications that require advanced transceiver support and hardened IP blocks. Series-level innovations include the HyperFlex core architecture, heterogeneous 3D SiP transceiver tiles, and high-speed transceiver technology suitable for chip-to-chip, chip-to-module, and backplane applications.

Key Features

- Core Architecture HyperFlex® core architecture innovations are part of the Stratix 10 TX family, delivering improved core performance for demanding logic designs.

- Logic Capacity 2,500,000 logic elements provide large-scale programmable resources for complex custom logic, state machines, and datapaths.

- On-chip Memory Total RAM bits: 204,472,320, enabling substantial local buffering and on-chip data storage for high-throughput pipelines.

- High-speed Transceivers (series-level) Stratix 10 TX devices support dual-mode transceivers capable of 57.8 Gbps PAM4 and 28.9 Gbps NRZ operation for high-bandwidth serial links and backplane connectivity.

- Interfaces & I/O 440 I/O pins provide flexible external connectivity for complex multi-channel systems and wide parallel interfaces.

- Power and Voltage Voltage supply range: 770 mV to 970 mV, allowing designers to target optimized power/performance operating points.

- Package & Mounting Surface-mount 2397-BBGA package (supplier device package: 2397-FBGA, 50 × 50 mm) for high-density board integration.

- Operating Conditions Extended grade device with an operating temperature range of 0 °C to 100 °C to suit many commercial and server-class environments.

- Hardened IP and System Features (series-level) Stratix 10 TX family includes hardened IP such as PCI Express Gen3 and multi-rate Ethernet MACs with FEC to support standard high-speed interfaces.

Typical Applications

- High-speed networking and switching Use the device's large logic capacity, on-chip memory, and series transceiver capabilities to implement packet processing, switching fabrics, and line-rate forwarding.

- Backplane and module connectivity Dual-mode transceiver support and high I/O count make the device suitable for chip-to-chip, chip-to-module, and backplane signal and data aggregation tasks.

- Server and data center acceleration Deploy the FPGA fabric and large on-chip memory for custom acceleration, offload engines, and protocol bridging in compute and storage systems.

- PCI Express-based systems Leverage series-level hardened PCIe Gen3 IP for host and add-in card applications requiring high-throughput low-latency links.

Unique Advantages

- Massive programmable fabric: 2,500,000 logic elements enable implementation of large, integrated hardware functions without distributing logic across multiple devices.

- Extensive on-chip memory: 204,472,320 total RAM bits reduce dependence on external memory for mid-sized data buffering and accelerate in-line processing.

- High-density I/O: 440 I/O pins support wide parallel buses and multiple serial/parallel interfaces for versatile system integration.

- Advanced packaging: 2397-FBGA 50 × 50 mm package enables high pin-count, high-density board designs while supporting the Stratix 10 TX family’s heterogeneous packaging technologies.

- Power tuning capability: A defined supply range of 770 mV to 970 mV provides design flexibility for optimizing power versus performance.

- Extended operating range: Rated 0 °C to 100 °C for deployment in commercial and server-class environments where extended-grade operation is required.

Why Choose 1ST250EU2F50E2VG?

The 1ST250EU2F50E2VG places a high-capacity Stratix 10 TX FPGA fabric into a compact 2397-BBGA package, combining 2.5 million logic elements, large on-chip memory, and a high I/O count for demanding system designs. It is positioned for engineers building high-bandwidth networking, backplane connectivity, PCIe-enabled systems, and data-center acceleration platforms that require a large, integrated programmable resource.

Choosing this device provides a scalable platform with series-level innovations—such as HyperFlex architecture and high-speed transceiver technology—supported by a comprehensive FPGA family. The combination of logic density, memory capacity, and interface flexibility delivers long-term design headroom and integration potential for evolving system requirements.

Request a quote or contact sales to discuss availability, pricing, and technical evaluation of 1ST250EU2F50E2VG for your next high-performance FPGA design.

Date Founded: 1968

Headquarters: Santa Clara, California, USA

Employees: 130,000+

Revenue: $54.23 Billion

Certifications and Memberships: ISO9001:2015, ISO14001:2015, ISO17025:2017, ISO27001:2022, ISO45001:2018, ISO50001:2018