1ST280EY1F55I2LG

| Part Description |

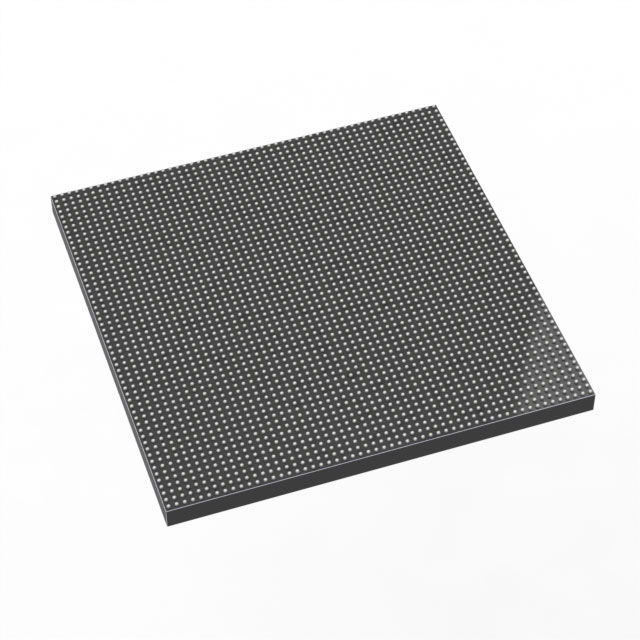

Stratix® 10 TX Field Programmable Gate Array (FPGA) IC 296 2800000 2912-BBGA, FCBGA |

|---|---|

| Quantity | 1,188 Available (as of May 5, 2026) |

| Product Category | Field Programmable Gate Array (FPGA) |

|---|---|

| Manufacturer | Intel |

| Manufacturing Status | Active |

| Manufacturer Standard Lead Time | 12 Weeks |

| Datasheet |

Specifications & Environmental

| Device Package | 2912-FBGA, FC (55x55) | Grade | Industrial | Operating Temperature | -40°C – 100°C | ||

|---|---|---|---|---|---|---|---|

| Package / Case | 2912-BBGA, FCBGA | Number of I/O | 296 | Voltage | 820 mV - 880 mV | ||

| Mounting Method | Surface Mount | RoHS Compliance | Unknown | REACH Compliance | REACH Unaffected | ||

| Moisture Sensitivity Level | 3 (168 Hours) | Number of LABs/CLBs | 350000 | Number of Logic Elements/Cells | 2800000 | ||

| Number of Gates | N/A | ECCN | N/A | HTS Code | N/A | ||

| Qualification | N/A | Total RAM Bits | 240123904 |

Overview of 1ST280EY1F55I2LG – Stratix® 10 TX FPGA, 2.8M Logic Elements

The 1ST280EY1F55I2LG is an Intel Stratix® 10 TX field programmable gate array (FPGA) in a 2912-BBGA FCBGA package. It integrates a high-performance HyperFlex® core architecture and a monolithic 14 nm FPGA fabric, delivering large programmable logic capacity and extensive high-speed I/O for demanding communications, data center, and networking designs.

Designed for applications that require high transceiver bandwidth, large on-chip memory, and hardened interface IP, this device balances performance, integration, and industrial-grade operating range to support complex system-level implementations.

Key Features

- Core Architecture HyperFlex® core architecture implemented in Intel 14 nm FinFET process; documented to deliver 2× the core performance compared to previous-generation high-performance FPGAs.

- Logic Capacity 2,800,000 logic elements (LEs) to implement large, complex logic designs and system-level integration.

- On‑Chip Memory 240,123,904 total RAM bits; series includes M20K internal SRAM blocks and select devices can include embedded eSRAM (47.25 Mbit) for large on-chip storage.

- High‑Speed Transceivers & Interfaces Dual-mode transceivers supporting 57.8 Gbps PAM4 and 28.9 Gbps NRZ operation; series supports up to 144 full-duplex transceiver channels and includes hardened PCI Express Gen3 and 10/25/100 Gbps Ethernet MAC IP with Reed‑Solomon FEC.

- DSP and Processor Options Hardened floating-point DSP blocks and variable precision DSP resources for signal processing; select devices include an embedded quad-core 64-bit Arm® Cortex‑A53 hard processor system (HPS) for application-class processing.

- I/O and Packaging 296 programmable I/O signals in a 2912-BBGA (2912-FBGA, FC 55×55) surface-mount package, supporting dense board-level integration.

- Power and Thermal Documented core supply voltage range of 820 mV to 880 mV and industrial operating temperature range from −40°C to 100°C to meet robust deployment conditions.

- Compliance RoHS compliant device and configured for surface-mount assembly.

Typical Applications

- High‑Speed Networking Implements 10/25/100 Gbps Ethernet and Reed‑Solomon FEC IP for routers, switches, and line cards that require dense MAC and transceiver integration.

- Telecom & Optical Transport Supports PAM4 and NRZ dual-mode transceivers and large aggregate bandwidth for backplane, chip-to-module, and chip-to-chip transport designs.

- Data Center Acceleration Large logic and memory resources plus hardened PCIe Gen3 IP enable FPGA-based acceleration and offload functions in server and appliance deployments.

- Signal Processing & DSP Systems Variable precision and floating-point DSP blocks provide the compute fabric needed for high-throughput signal processing and multi-channel data-paths.

Unique Advantages

- Highly integrated fabric: Monolithic 14 nm FPGA core combined with heterogeneous transceiver tiles consolidates logic, memory, and high-speed I/O in a single device to reduce board-level complexity.

- Massive logic and memory: 2.8 million logic elements and 240,123,904 RAM bits enable consolidation of multiple functions into one FPGA, reducing BOM and inter-chip latency.

- Flexible, high-throughput connectivity: Dual-mode transceivers up to 57.8 Gbps PAM4 and 28.9 Gbps NRZ plus hardened Ethernet and PCIe IP accelerate time-to-market for high-bandwidth interfaces.

- System-level performance options: Hardened DSP blocks and optional quad-core Arm Cortex‑A53 HPS provide both hardware acceleration and application-class processing on the same device.

- Industrial operating range: Documented −40°C to 100°C operating temperature and surface-mount 2912-BBGA packaging support deployment in robust environments.

Why Choose 1ST280EY1F55I2LG?

The 1ST280EY1F55I2LG Stratix® 10 TX FPGA is positioned for designs that demand substantial programmable logic, extensive on-chip memory, and advanced high-speed serial connectivity. Its HyperFlex® architecture and 14 nm implementation provide the raw logic performance needed for large designs, while hardened IP blocks and dual-mode transceivers simplify integration of industry-standard interfaces.

This device is suited to systems engineering teams and procurement focused on high-bandwidth networking, telecom transport, data center acceleration, and complex signal processing applications that benefit from consolidated logic, memory, and transceiver resources within an industrial temperature-rated package.

Request a quote or submit an inquiry to obtain pricing, lead-time, and availability for 1ST280EY1F55I2LG.

Date Founded: 1968

Headquarters: Santa Clara, California, USA

Employees: 130,000+

Revenue: $54.23 Billion

Certifications and Memberships: ISO9001:2015, ISO14001:2015, ISO17025:2017, ISO27001:2022, ISO45001:2018, ISO50001:2018