1ST280EY2F55I2VG

| Part Description |

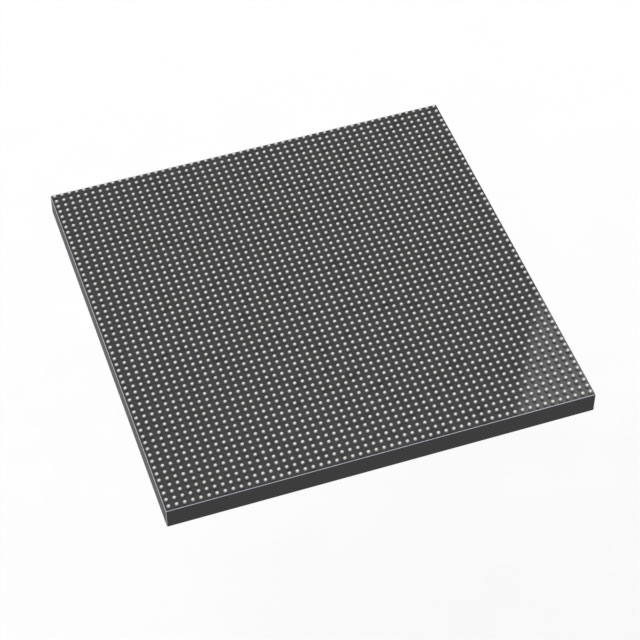

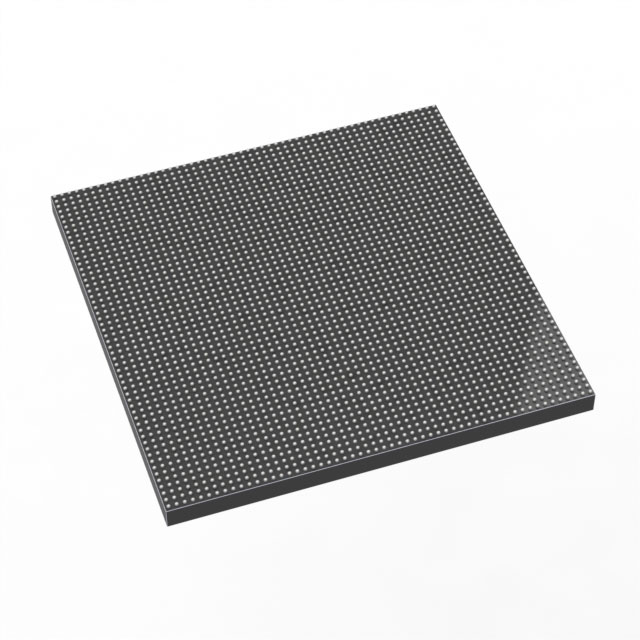

Stratix® 10 TX Field Programmable Gate Array (FPGA) IC 296 2800000 2912-BBGA, FCBGA |

|---|---|

| Quantity | 1,038 Available (as of May 5, 2026) |

| Product Category | Field Programmable Gate Array (FPGA) |

|---|---|

| Manufacturer | Intel |

| Manufacturing Status | Active |

| Manufacturer Standard Lead Time | 12 Weeks |

| Datasheet |

Specifications & Environmental

| Device Package | 2912-FBGA, FC (55x55) | Grade | Industrial | Operating Temperature | -40°C – 100°C | ||

|---|---|---|---|---|---|---|---|

| Package / Case | 2912-BBGA, FCBGA | Number of I/O | 296 | Voltage | 770 mV - 970 mV | ||

| Mounting Method | Surface Mount | RoHS Compliance | Unknown | REACH Compliance | REACH Unaffected | ||

| Moisture Sensitivity Level | 3 (168 Hours) | Number of LABs/CLBs | 350000 | Number of Logic Elements/Cells | 2800000 | ||

| Number of Gates | N/A | ECCN | N/A | HTS Code | N/A | ||

| Qualification | N/A | Total RAM Bits | 240123904 |

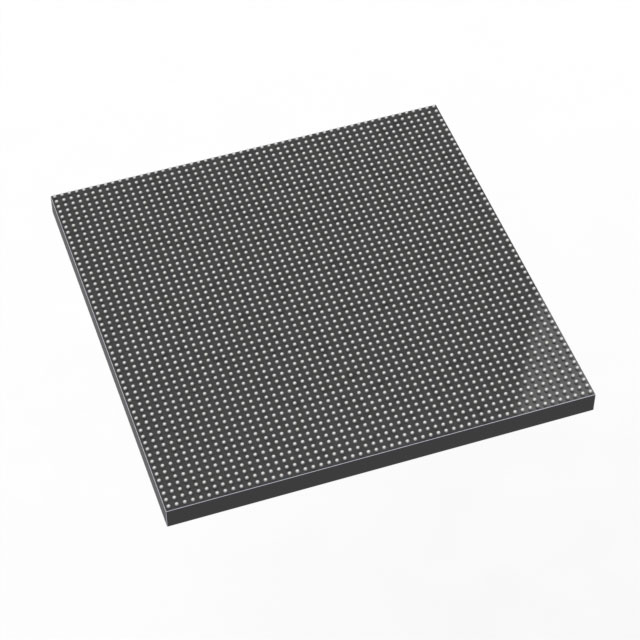

Overview of 1ST280EY2F55I2VG – Stratix® 10 TX Field Programmable Gate Array (FPGA), 2,800,000 Logic Elements, 2912‑BBGA

The 1ST280EY2F55I2VG is an Intel Stratix® 10 TX FPGA in a 2912‑ball FCBGA package, offering a monolithic high‑density fabric with 2,800,000 logic elements and extensive on‑chip RAM. Built around the Stratix 10 TX family architecture, the device targets high‑bandwidth networking, telecom and data‑center designs that require large programmable fabric, high‑speed transceivers, and industrial temperature operation.

Stratix 10 TX family innovations referenced in the device overview include the Intel HyperFlex™ core architecture, heterogeneous transceiver tiles with dual‑mode PAM4/NRZ capability, and hardened protocol IP such as PCI Express Gen3 and high‑speed Ethernet MAC. This part combines dense logic, substantial embedded memory and broad I/O in a 55×55 mm FBGA surface‑mount package.

Key Features

- Core Architecture Intel HyperFlex™ core architecture with a monolithic 14 nm FPGA fabric delivering 2,800,000 logic elements for large, compute‑intensive designs.

- High‑Speed Transceivers Family transceiver technology supports dual‑mode operation: up to 57.8 Gbps PAM4 and 28.9 Gbps NRZ data rates, with the family offering up to 144 full‑duplex transceiver channels (as described in the device overview).

- On‑Chip Memory 240,123,904 total RAM bits providing substantial embedded storage for buffering, packet handling, and algorithmic state.

- Interfaces & Hardened IP Supports hardened IP blocks described for the Stratix 10 TX family, including PCI Express Gen3 and 10/25/100 Gbps Ethernet MAC with dedicated FEC options.

- I/O Density 296 I/O pins to support broad external connectivity and system interface flexibility.

- Power & Voltage Core voltage supply range of 770 mV to 970 mV to match system power domains and enable power management strategies.

- Package & Mounting 2912‑ball BBGA (FCBGA) supplier package (2912‑FBGA, 55×55 mm) in a surface‑mount form factor for high‑density board designs.

- Operating Conditions & Compliance Industrial operating temperature range of −40 °C to 100 °C and RoHS compliance for regulatory and environmental alignment.

Typical Applications

- High‑Bandwidth Networking Packet processing, switching and aggregation where large programmable fabric and high transceiver bandwidth accelerate data‑path logic and protocol offload.

- Telecom & Optical Transport Backplane and module designs leveraging dual‑mode PAM4/NRZ transceivers and hardened Ethernet/PCIe IP for linecard and transport equipment.

- Data Center & Storage Accelerator and interface controllers that require dense logic, large on‑chip memory, and heavy I/O to meet throughput and buffering demands.

- High‑Performance Embedded Systems Compute‑intensive embedded applications that combine programmable logic with advanced memory and I/O to implement custom processing pipelines.

Unique Advantages

- High Logic Density: 2,800,000 logic elements enable complex system implementations and large-scale parallelism without external logic expansion.

- Substantial On‑Chip Memory: 240,123,904 bits of embedded RAM reduce dependence on external memory for buffering and intermediate storage.

- Advanced Transceiver Capability: Dual‑mode PAM4/NRZ transceiver technology described for the family supports high aggregate bandwidth requirements for modern links.

- Extensive I/O Count: 296 I/O pins provide broad connectivity options for external devices, memory, and system interfaces.

- Industrial Temperature Range and RoHS Compliance: −40 °C to 100 °C operation and RoHS compliance support deployment in industrial environments with regulatory alignment.

- Compact High‑Density Package: 2912‑ball FCBGA (55×55 mm) surface‑mount package balances high integration with a manageable PCB footprint for dense system boards.

Why Choose 1ST280EY2F55I2VG?

The 1ST280EY2F55I2VG combines a high‑performance Stratix 10 TX fabric with a large on‑chip memory pool and extensive I/O to address demanding, bandwidth‑heavy designs. Its family‑level innovations—HyperFlex core architecture and advanced transceiver tiles—provide a platform suited for networking, telecom and data‑center applications that need programmable throughput and integration.

This device is positioned for engineers and system designers who require scalable logic capacity, substantial embedded RAM, and industrial temperature operation in a single, surface‑mount FBGA package. Its feature set supports long‑lifecycle projects that benefit from a robust FPGA ecosystem and hardened protocol IP available in the Stratix 10 TX family.

Request a quote or submit an inquiry to our sales team to discuss pricing, availability, and how 1ST280EY2F55I2VG can fit your next high‑performance design.

Date Founded: 1968

Headquarters: Santa Clara, California, USA

Employees: 130,000+

Revenue: $54.23 Billion

Certifications and Memberships: ISO9001:2015, ISO14001:2015, ISO17025:2017, ISO27001:2022, ISO45001:2018, ISO50001:2018