EP1SGX25DF672C6

| Part Description |

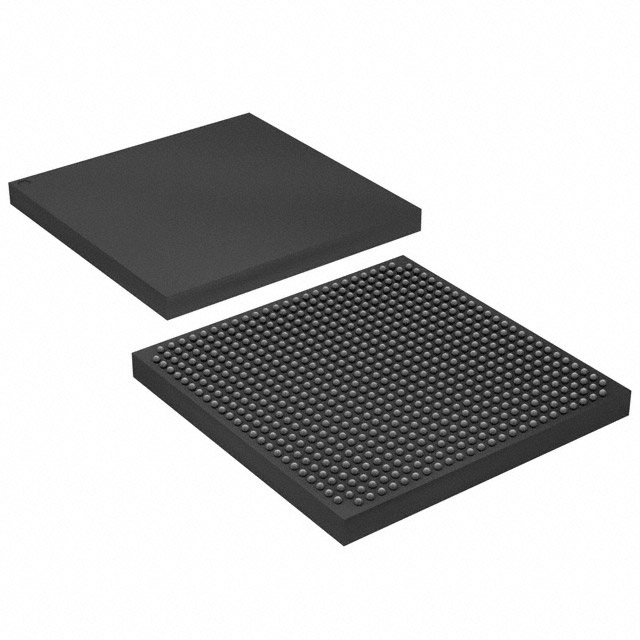

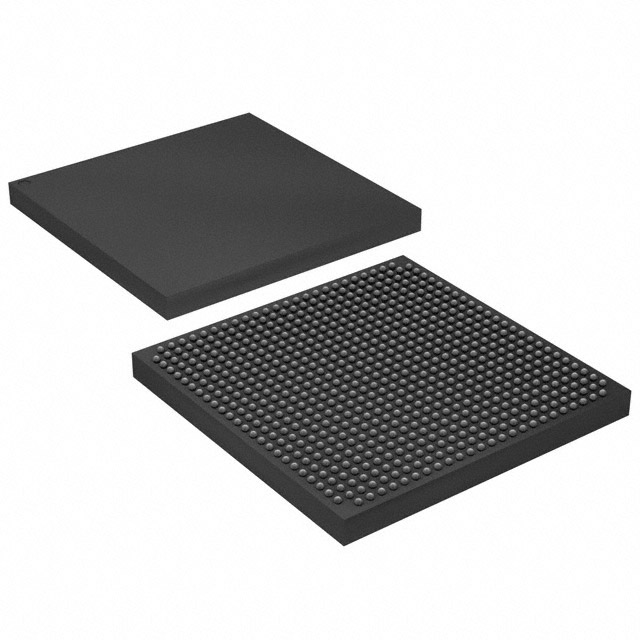

Stratix® GX Field Programmable Gate Array (FPGA) IC 455 1944576 25660 672-BBGA |

|---|---|

| Quantity | 168 Available (as of May 5, 2026) |

| Product Category | Field Programmable Gate Array (FPGA) |

|---|---|

| Manufacturer | Intel |

| Manufacturing Status | Obsolete |

| Manufacturer Standard Lead Time | RFQ |

| Datasheet |

Specifications & Environmental

| Device Package | 672-FBGA (27x27) | Grade | Commercial | Operating Temperature | 0°C – 85°C | ||

|---|---|---|---|---|---|---|---|

| Package / Case | 672-BBGA | Number of I/O | 455 | Voltage | 1.425 V - 1.575 V | ||

| Mounting Method | Surface Mount | RoHS Compliance | RoHS non-compliant | REACH Compliance | REACH Unknown | ||

| Moisture Sensitivity Level | 3 (168 Hours) | Number of LABs/CLBs | 2566 | Number of Logic Elements/Cells | 25660 | ||

| Number of Gates | N/A | ECCN | 3A001A7A | HTS Code | 8542.39.0001 | ||

| Qualification | N/A | Total RAM Bits | 1944576 |

Overview of EP1SGX25DF672C6 – Stratix® GX FPGA IC, 25,660 Logic Elements, 672‑BBGA

The EP1SGX25DF672C6 is a Stratix® GX family field-programmable gate array (FPGA) in a 672‑BBGA package designed for high-performance logic integration and high-speed serial connectivity. Built on the Stratix GX architecture, this commercial-grade device delivers 25,660 logic elements and approximately 1.94 Mbits of on‑chip RAM for complex digital signal processing, protocol bridging, and high-speed interface designs.

With an I/O count of 455 and support for the Stratix GX family’s high-speed transceiver technology, this device is suited to applications requiring dense I/O, embedded memory, and integrated SERDES/transceiver features while operating within a 1.425 V to 1.575 V supply window at commercial temperatures (0 °C to 85 °C).

Key Features

- Logic Capacity — 25,660 logic elements provide substantial programmable logic resources for complex control, processing, and glue‑logic functions.

- Embedded Memory — Approximately 1.94 Mbits of on‑chip RAM (1,944,576 bits) with TriMatrix™ memory architecture for flexible dual-port memory and FIFO implementations.

- High‑Speed Transceiver Technology — Stratix GX family transceivers support clock data recovery (CDR) and embedded SERDES with serial data rates from 500 Mbps up to 3.1875 Gbps and family support for 4–20 transceiver channels.

- Protocol and Signal‑Integrity Features — Family-level support for protocols such as XAUI, Gigabit Ethernet, and SONET/SDH, plus programmable VOD, pre‑emphasis, and equalization to optimize high‑speed links.

- I/O Density — 455 user I/Os to support broad interfacing options and high pin-count system designs.

- DSP and Clocking Resources — Family features include high‑speed DSP blocks (multiply/multiply‑accumulate faster than 300 MHz) and up to eight general-purpose PLLs for flexible clock management.

- Package & Mounting — 672‑BBGA surface‑mount package (supplier package: 672‑FBGA, 27 × 27 mm) for space-efficient board designs.

- Power & Temperature — Nominal supply range 1.425 V to 1.575 V; commercial operating grade with specified operation from 0 °C to 85 °C.

- Compliance — RoHS‑compliant for environmental and manufacturing compliance.

Typical Applications

- High‑speed backplane interfaces — Use the device’s transceiver bandwidth and dense I/O to implement multi‑lane backplane links and protocol bridging.

- Chip‑to‑chip interconnects — Embedded SERDES and CDR capabilities enable reliable high‑speed serial links between devices and modules.

- Communications protocol bridging — Programmable logic and transceiver features support implementation of protocol converters and packet processing functions.

- High‑performance DSP and filtering — On‑chip DSP blocks and abundant logic elements enable FIR filters, MAC operations, and other signal‑processing engines.

Unique Advantages

- Integrated high‑speed serial capability: Family transceivers with CDR and SERDES at up to 3.1875 Gbps simplify high‑bandwidth link implementation and reduce external PHY requirements.

- Substantial programmable resources: 25,660 logic elements and approximately 1.94 Mbits of embedded RAM support complex algorithms and multi‑function designs on a single device.

- High I/O count for system integration: 455 I/Os enable direct interfacing to multiple peripherals, memory devices, and high‑speed buses, reducing glue logic.

- Flexible clocking and DSP support: Dedicated PLLs and high‑speed DSP blocks provide deterministic timing and efficient signal processing implementation.

- Compact board footprint: 672‑BBGA (27 × 27 mm) surface‑mount package delivers high integration density for space‑constrained systems.

- Commercial‑grade and RoHS‑compliant: Designed for 0 °C to 85 °C operation and compliant with RoHS manufacturing requirements.

Why Choose EP1SGX25DF672C6?

The EP1SGX25DF672C6 delivers a balance of substantial programmable logic, embedded memory, and high‑speed transceiver technology from the Stratix GX family in a compact 672‑BBGA package. Its combination of 25,660 logic elements, approximately 1.94 Mbits of on‑chip RAM, and 455 I/Os makes it well suited for designers implementing high‑bandwidth interfaces, protocol bridging, and DSP‑intensive functions within commercial temperature ranges.

For teams needing scalable FPGA resources with integrated SERDES/transceiver features and a broad set of family‑level protocol and signal‑integrity capabilities, this device provides a platform that reduces external component count and consolidates system functionality while supporting established development flows for Stratix GX devices.

Request a quote or submit a sales inquiry to evaluate EP1SGX25DF672C6 for your next high‑performance FPGA design.

Date Founded: 1968

Headquarters: Santa Clara, California, USA

Employees: 130,000+

Revenue: $54.23 Billion

Certifications and Memberships: ISO9001:2015, ISO14001:2015, ISO17025:2017, ISO27001:2022, ISO45001:2018, ISO50001:2018