EP2SGX30CF780C3N

| Part Description |

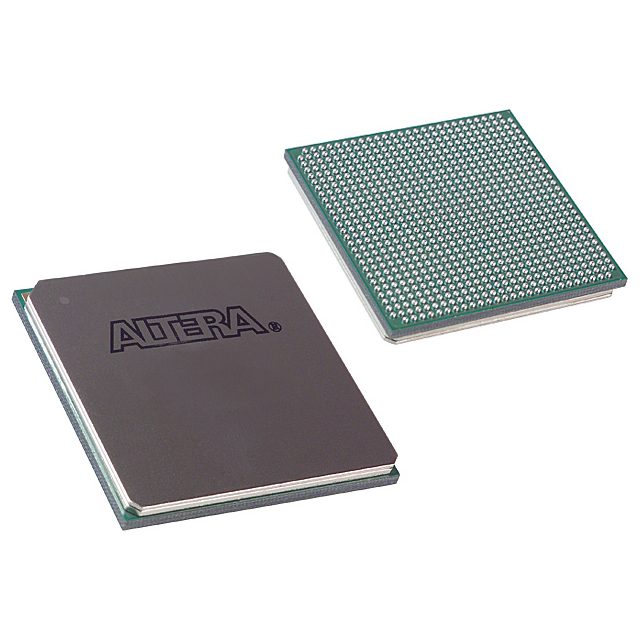

Stratix® II GX Field Programmable Gate Array (FPGA) IC 361 1369728 33880 780-BBGA |

|---|---|

| Quantity | 667 Available (as of May 5, 2026) |

| Product Category | Field Programmable Gate Array (FPGA) |

|---|---|

| Manufacturer | Intel |

| Manufacturing Status | Obsolete |

| Manufacturer Standard Lead Time | RFQ |

| Datasheet |

Specifications & Environmental

| Device Package | 780-FBGA (29x29) | Grade | Commercial | Operating Temperature | 0°C – 85°C | ||

|---|---|---|---|---|---|---|---|

| Package / Case | 780-BBGA | Number of I/O | 361 | Voltage | 1.15 V - 1.25 V | ||

| Mounting Method | Surface Mount | RoHS Compliance | RoHS Compliant | REACH Compliance | REACH Unaffected | ||

| Moisture Sensitivity Level | 3 (168 Hours) | Number of LABs/CLBs | 1694 | Number of Logic Elements/Cells | 33880 | ||

| Number of Gates | N/A | ECCN | 3A991D | HTS Code | 8542.39.0001 | ||

| Qualification | N/A | Total RAM Bits | 1369728 |

Overview of EP2SGX30CF780C3N – Stratix II GX FPGA – 780‑BBGA

The EP2SGX30CF780C3N is a Stratix® II GX field‑programmable gate array in a 780‑ball BGA package designed for high‑performance, high‑bandwidth digital designs. Built on the Stratix II GX architecture, this device combines a large logic array, embedded memory, and the family’s high‑speed transceiver and DSP capabilities aimed at communications, interface bridging, and high‑speed I/O applications.

With 33,880 logic elements, approximately 1.37 Mbits of embedded memory, and 361 user I/O pins, the device targets system designs that require significant logic capacity, on‑chip memory, and flexible I/O connectivity while operating within a commercial temperature range and a 1.15 V–1.25 V core supply.

Key Features

- Core logic — 33,880 logic elements providing significant programmable logic capacity for complex control, protocol, and datapath implementations.

- Logic array blocks — 1,694 logic array blocks for structured logic partitioning and predictable resource allocation.

- Embedded memory — Approximately 1.37 Mbits of on‑chip RAM to support FIFOs, packet buffering, and local data storage.

- I/O and package — 361 user I/O pins in a 780‑BBGA (780‑FBGA, 29×29) surface‑mount package for dense external connectivity.

- Stratix II GX family transceiver architecture — Family features include high‑speed serial transceivers with clock and data recovery and SERDES capability supporting multi‑Gbps operation (family‑level capability described in datasheet).

- DSP and clocking — Family‑level DSP blocks and up to four enhanced PLLs provide dedicated multiplier/accumulate resources and flexible clock management (family features as described in the Stratix II GX device handbook).

- Supply and temperature — 1.15 V to 1.25 V core supply range and commercial operating temperature from 0 °C to 85 °C, suitable for a wide range of standard electronic applications.

- Mounting and compliance — Surface‑mount BGA package; RoHS compliant.

Typical Applications

- High‑speed backplane and interface bridges — Leverages Stratix II GX serial transceiver family features and large logic/memory resources to implement protocol bridging and backplane interfaces.

- Chip‑to‑chip interconnects — On‑chip SERDES and extensive I/O enable high‑bandwidth links between devices in multi‑chip systems.

- Communications equipment — Embedded memory and DSP resources support buffering, packet processing, and signal processing functions commonly required in communications systems.

Unique Advantages

- Substantial programmable logic capacity: 33,880 logic elements allow implementation of large, complex logic designs without immediately requiring external FPGA resources.

- On‑chip RAM for buffering: Approximately 1.37 Mbits of embedded memory reduces dependence on external memory for intermediate buffering and FIFOs.

- Extensive I/O in a compact package: 361 I/O pins in a 780‑ball BGA provide high pin count and dense routing for systems needing many external interfaces.

- Commercial temperature and RoHS compliance: Designed for standard commercial deployments with lead‑free, RoHS‑compliant construction.

- Stratix II GX architecture benefits: Family features such as high‑speed transceivers, DSP blocks, and advanced PLL options offer a versatile platform for high‑performance designs (as described in the device handbook).

Why Choose EP2SGX30CF780C3N?

The EP2SGX30CF780C3N positions itself as a versatile Stratix II GX device combining substantial logic density, embedded memory, and a high I/O count in a 780‑BBGA package. It is well suited for engineers building communications interfaces, protocol bridges, and other systems that require programmable logic with on‑chip memory and family‑level high‑speed transceiver capabilities.

Choosing this device gives designers access to the Stratix II GX architecture benefits—scalable clocking, DSP resources, and transceiver features—while keeping power and system integration predictable through documented supply and temperature limits and RoHS compliance.

Request a quote or submit an inquiry to receive pricing, availability, and additional technical support information for EP2SGX30CF780C3N.

Date Founded: 1968

Headquarters: Santa Clara, California, USA

Employees: 130,000+

Revenue: $54.23 Billion

Certifications and Memberships: ISO9001:2015, ISO14001:2015, ISO17025:2017, ISO27001:2022, ISO45001:2018, ISO50001:2018