EP3C16E144C8

| Part Description |

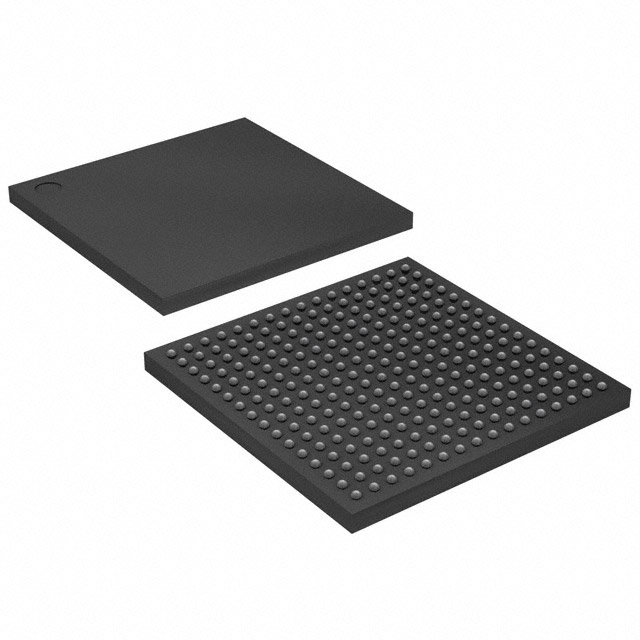

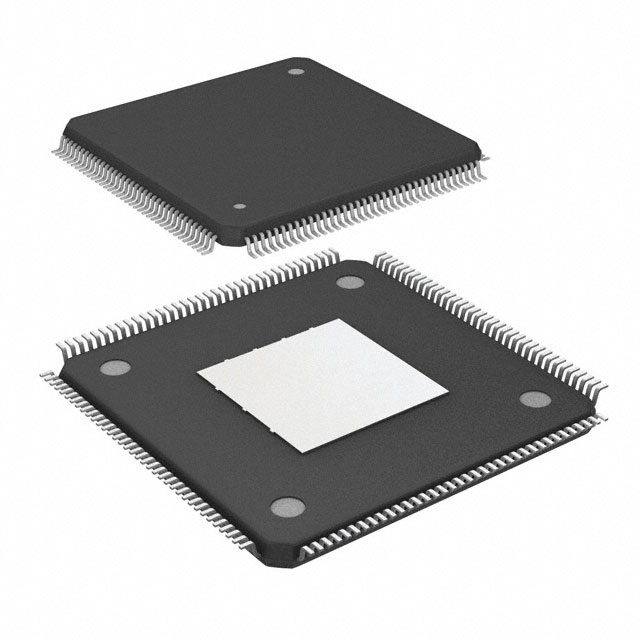

Cyclone® III Field Programmable Gate Array (FPGA) IC 84 516096 15408 144-LQFP Exposed Pad |

|---|---|

| Quantity | 223 Available (as of May 5, 2026) |

| Product Category | Field Programmable Gate Array (FPGA) |

|---|---|

| Manufacturer | Intel |

| Manufacturing Status | Last Time Buy |

| Manufacturer Standard Lead Time | 26 Weeks |

| Datasheet |

Specifications & Environmental

| Device Package | 144-EQFP (20x20) | Grade | Commercial | Operating Temperature | 0°C – 85°C | ||

|---|---|---|---|---|---|---|---|

| Package / Case | 144-LQFP Exposed Pad | Number of I/O | 84 | Voltage | 1.15 V - 1.25 V | ||

| Mounting Method | Surface Mount | RoHS Compliance | RoHS non-compliant | REACH Compliance | REACH Unaffected | ||

| Moisture Sensitivity Level | 3 (168 Hours) | Number of LABs/CLBs | 963 | Number of Logic Elements/Cells | 15408 | ||

| Number of Gates | N/A | ECCN | 3A991D | HTS Code | 8542.39.0001 | ||

| Qualification | N/A | Total RAM Bits | 516096 |

Overview of EP3C16E144C8 – Cyclone® III FPGA, 15,408 logic elements, 84 I/Os (144-LQFP)

The EP3C16E144C8 is a Cyclone® III family field-programmable gate array (FPGA) offered in a 144-LQFP exposed-pad surface-mount package. It delivers a balance of functionality and low power for high-volume, cost-sensitive designs that require moderate logic density, embedded memory, and flexible I/O.

Built on the Cyclone III device family architecture, this device targets applications that benefit from low static power, integrated clock management, and a high memory-to-logic ratio while operating within commercial temperature and supply ranges.

Key Features

- Logic 15,408 logic elements provide the programmable fabric needed for custom digital logic, control, and glue-logic implementations.

- Embedded memory 516,096 bits of on-chip RAM (approximately 0.5 Mbits) to support buffering, FIFOs, and local data storage without external memory for many use cases.

- I/O count and flexibility 84 available I/Os with support for a wide range of I/O standards commonly supported by the Cyclone III family, enabling interface to diverse peripherals and buses.

- Clock management Four phase-locked loops (PLLs) per device with five outputs per PLL; PLLs are cascadable and dynamically reconfigurable for flexible clock synthesis and domain generation.

- Low-power family attributes Cyclone III family devices are designed using a low-power process and silicon optimizations to minimize power consumption; family documentation cites very low static power operation suitable for thermally constrained and battery-powered systems.

- Supply and operating range Core voltage requirement 1.15 V to 1.25 V; commercial operating temperature range 0 °C to 85 °C.

- Package & mounting 144-LQFP exposed pad (supplier device package listed as 144-EQFP, 20 × 20); surface-mount mounting for compact PCB integration and thermal pad support.

- Integration & IP support Part of the Cyclone III family with access to the family’s IP ecosystem and embedded processing options (Nios® II is available for the family), enabling accelerated development with pre‑verified cores.

- RoHS compliant Meets RoHS requirements for lead-free assembly and environmental compliance.

Typical Applications

- Portable and battery-powered devices Low static power characteristics help extend battery life and reduce cooling demands in handheld and portable systems.

- High-volume consumer and cost-sensitive products Suited for designs where a balance of functionality, low power, and cost drives the BOM and production choices.

- Interface and protocol bridging High I/O count and flexible I/O standard support make the device useful for protocol conversion, bridge functions, and peripheral aggregation.

- Embedded control and upgradeable systems Integrated clock management and family-level support for remote system upgrade workflows enable adaptable embedded control designs.

Unique Advantages

- Moderate, usable logic capacity: 15,408 logic elements provide a practical resource pool for mid-range custom logic without the cost or power of larger FPGAs.

- On-chip memory available: 516,096 bits of embedded RAM reduce dependence on external memory for buffering and local storage, simplifying PCB design.

- Flexible clocking: Multiple PLLs with cascaded outputs and dynamic reconfiguration options simplify multi‑clock domain designs and I/O timing management.

- Low-power family design: Cyclone III family attributes and low-power process technology help meet tight power budgets for thermally constrained or battery-operated products.

- Compact, serviceable package: 144-LQFP exposed-pad surface-mount package provides a small footprint with thermal pad support for better heat dissipation on compact PCBs.

- Developer ecosystem: Family-level support for IP cores and embedded processor options accelerates development and reduces integration effort.

Why Choose EP3C16E144C8?

The EP3C16E144C8 offers a balanced solution for designers who need a mid-range FPGA with meaningful on-chip memory, robust clocking resources, and a flexible I/O set in a compact 144-LQFP package. Its family-level low-power characteristics and support ecosystem make it well suited to cost- and power-sensitive applications that require reliable programmable logic and straightforward integration.

This device is ideal for engineering teams building portable devices, interface concentrators, or embedded control systems that operate within commercial temperature limits and standard core-voltage requirements. The combination of logic capacity, embedded RAM, and clock-management features delivers long-term design flexibility and reduces external component count.

Request a quote or submit a purchase inquiry to receive pricing, availability, and lead-time information for the EP3C16E144C8.

Date Founded: 1968

Headquarters: Santa Clara, California, USA

Employees: 130,000+

Revenue: $54.23 Billion

Certifications and Memberships: ISO9001:2015, ISO14001:2015, ISO17025:2017, ISO27001:2022, ISO45001:2018, ISO50001:2018