EP3C25E144C7

| Part Description |

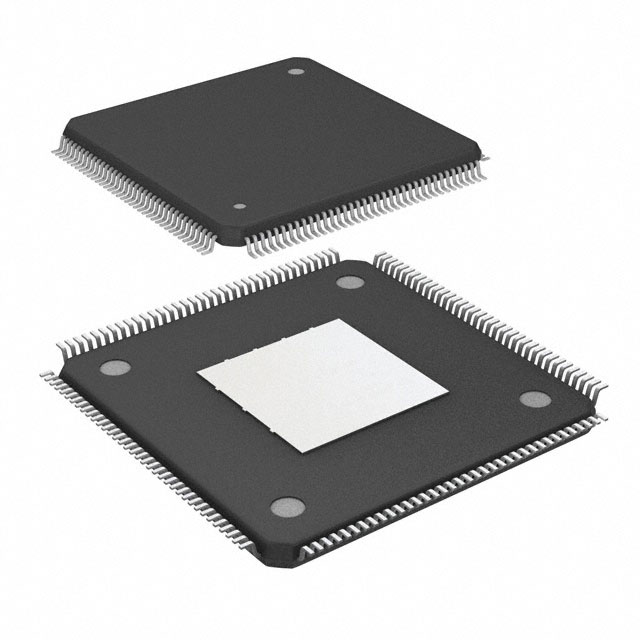

Cyclone® III Field Programmable Gate Array (FPGA) IC 82 608256 24624 144-LQFP Exposed Pad |

|---|---|

| Quantity | 1,788 Available (as of May 5, 2026) |

| Product Category | Field Programmable Gate Array (FPGA) |

|---|---|

| Manufacturer | Intel |

| Manufacturing Status | Last Time Buy |

| Manufacturer Standard Lead Time | 26 Weeks |

| Datasheet |

Specifications & Environmental

| Device Package | 144-EQFP (20x20) | Grade | Commercial | Operating Temperature | 0°C – 85°C | ||

|---|---|---|---|---|---|---|---|

| Package / Case | 144-LQFP Exposed Pad | Number of I/O | 82 | Voltage | 1.15 V - 1.25 V | ||

| Mounting Method | Surface Mount | RoHS Compliance | RoHS Compliant | REACH Compliance | REACH Unaffected | ||

| Moisture Sensitivity Level | 3 (168 Hours) | Number of LABs/CLBs | 1539 | Number of Logic Elements/Cells | 24624 | ||

| Number of Gates | N/A | ECCN | 3A991D | HTS Code | 8542.39.0001 | ||

| Qualification | N/A | Total RAM Bits | 608256 |

Overview of EP3C25E144C7 – Cyclone® III FPGA, 24,624 logic elements, 144-LQFP Exposed Pad

The EP3C25E144C7 is a Cyclone® III family Field Programmable Gate Array (FPGA) IC offering a balance of logic density, on-chip memory, and low-power operation for cost-sensitive, high-volume designs. Built on the Cyclone III device family architecture, it targets applications that require flexible I/O, moderate embedded memory, and efficient clock management while maintaining a commercial temperature grade.

Key value propositions include a dense logic fabric (24,624 logic elements), approximately 0.61 Mbits of embedded memory, and family-level low-power optimizations suited to designs where power, integration, and board-level I/O are important.

Key Features

- Logic Density — 24,624 logic elements provide substantial programmable logic resources for mid-range FPGA designs.

- Embedded Memory — Approximately 0.61 Mbits (608,256 bits) of on-chip RAM to support buffering, small data structures, and state storage.

- I/O Capacity & Signal Integrity — 82 user I/O pins with family features such as adjustable I/O slew rates and multi-value on-chip termination (OCT) calibration to help maintain signal integrity across PVT conditions.

- Clock Management — Cyclone III family clocking capabilities including four phase-locked loops (PLLs) per device and multiple PLL outputs to support robust clock synthesis and distribution.

- Low-Power Architecture — Part of the Cyclone III family engineered with low-power process technology and design techniques to reduce static power consumption for battery-powered or thermally constrained systems.

- Power Supply & Operating Range — Core voltage range of 1.15 V to 1.25 V; commercial operating temperature from 0 °C to 85 °C.

- Package & Mounting — 144-LQFP Exposed Pad package; supplier device package listed as 144-EQFP (20×20). Surface-mount mounting type simplifies PCB assembly and thermal conduction via exposed pad.

- Compliance — RoHS compliant for regulatory and manufacturing alignment.

Typical Applications

- Consumer and Portable Electronics — Implement control logic, interface bridging, and custom peripherals where low-power operation and moderate logic density are required.

- Communications and Networking — Use for protocol bridging, packet buffering, and custom I/O adaptation leveraging the device’s PLL-based clock management and I/O flexibility.

- Industrial Control — Integrate motor control logic, sensor interfacing, and machine-state control in systems operating within commercial temperature ranges.

- Embedded Systems — Realize application-specific accelerators, glue logic, and compact system controllers that benefit from on-chip memory and dense logic resources.

Unique Advantages

- Highly integrated logic and memory: 24,624 logic elements combined with approximately 0.61 Mbits of embedded RAM reduce external component count and simplify board design.

- Power-conscious family architecture: Cyclone III’s low-power process and device-level optimizations help lower static power for thermally or battery-constrained products.

- Flexible clocking: Multiple PLLs and reconfigurable outputs enable robust clock domain creation and management without external clock-conditioning hardware.

- I/O versatility and signal integrity tools: Adjustable slew rates and OCT calibration support a wide range of signaling needs while helping to maintain signal quality across varying conditions.

- Compact, manufacturable package: 144-LQFP Exposed Pad with surface-mount mounting supports streamlined PCB assembly and improved thermal path through the exposed pad.

- Regulatory readiness: RoHS compliance aligns with standard manufacturing and environmental requirements.

Why Choose EP3C25E144C7?

The EP3C25E144C7 places Cyclone III family capabilities—significant logic resources, embedded memory, flexible I/O, and family-level low-power design—into a compact 144-LQFP Exposed Pad package. It is well suited for designers building mid-range FPGA-based systems that need a balance of integration, power efficiency, and I/O capability within a commercial temperature range.

Support from the Cyclone III device family resources and documentation helps accelerate development, integration of pre-built IP, and system validation, making this device a practical choice for cost-sensitive, high-volume designs that require dependable programmable logic functionality.

Request a quote or submit an inquiry to receive pricing and availability information for EP3C25E144C7.

Date Founded: 1968

Headquarters: Santa Clara, California, USA

Employees: 130,000+

Revenue: $54.23 Billion

Certifications and Memberships: ISO9001:2015, ISO14001:2015, ISO17025:2017, ISO27001:2022, ISO45001:2018, ISO50001:2018