EP3C80F780C7N

| Part Description |

Cyclone® III Field Programmable Gate Array (FPGA) IC 429 2810880 81264 780-BGA |

|---|---|

| Quantity | 105 Available (as of May 5, 2026) |

| Product Category | Field Programmable Gate Array (FPGA) |

|---|---|

| Manufacturer | Intel |

| Manufacturing Status | Active |

| Manufacturer Standard Lead Time | 26 Weeks |

| Datasheet |

Specifications & Environmental

| Device Package | 780-FBGA (29x29) | Grade | Commercial | Operating Temperature | 0°C – 85°C | ||

|---|---|---|---|---|---|---|---|

| Package / Case | 780-BGA | Number of I/O | 429 | Voltage | 1.15 V - 1.25 V | ||

| Mounting Method | Surface Mount | RoHS Compliance | RoHS Compliant | REACH Compliance | REACH Unaffected | ||

| Moisture Sensitivity Level | 3 (168 Hours) | Number of LABs/CLBs | 5079 | Number of Logic Elements/Cells | 81264 | ||

| Number of Gates | N/A | ECCN | 3A991D | HTS Code | 8542.39.0001 | ||

| Qualification | N/A | Total RAM Bits | 2810880 |

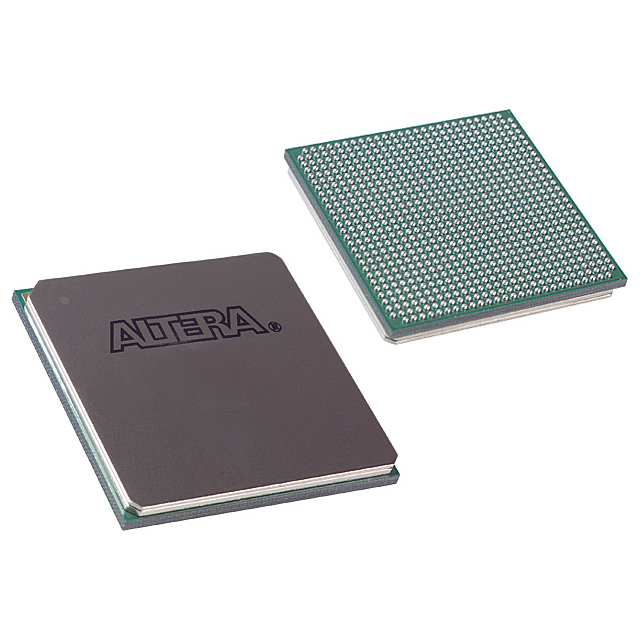

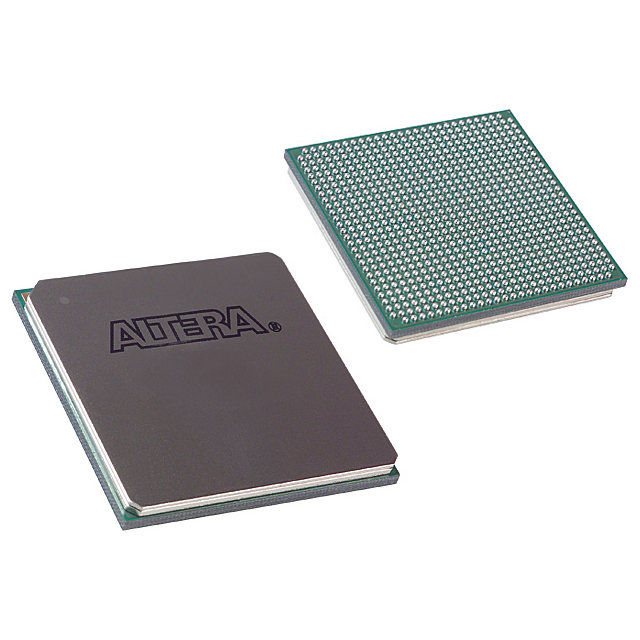

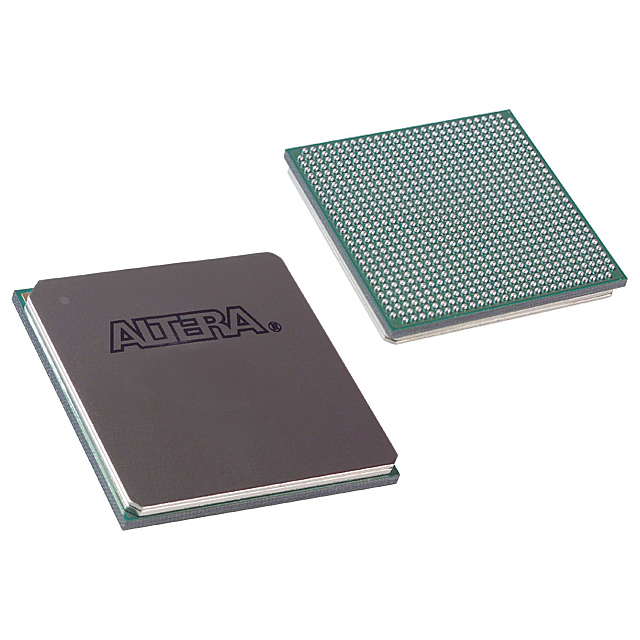

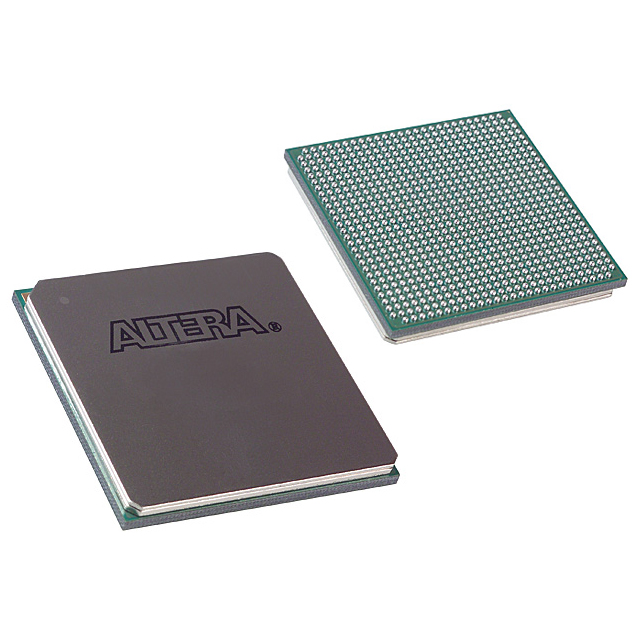

Overview of EP3C80F780C7N – Cyclone® III FPGA — 81,264 logic elements, 780‑BGA

The EP3C80F780C7N is an Intel Cyclone® III field programmable gate array (FPGA) offered in a 780‑ball fine‑pitch BGA package. It provides 81,264 logic elements, approximately 2.8 Mbits of embedded memory, and up to 429 general‑purpose I/O pins for mid‑range, I/O‑rich designs.

Designed for the Cyclone III device family, this device targets cost‑sensitive, low‑power, and high‑functionality applications where integration density, power efficiency, and flexible I/O are key design drivers.

Key Features

- Logic capacity 81,264 logic elements and 5,079 logic array blocks (LABs) provide substantial programmable logic for mid‑range designs.

- Embedded memory Approximately 2.8 Mbits of on‑chip RAM to support buffering, packet storage, and local data processing without external memory.

- I/O count and flexibility Up to 429 I/O pins support complex interfaces and high pin‑count system connectivity for diverse peripherals and buses.

- Clock management Cyclone III family architecture includes integrated PLL resources for flexible clock synthesis and management within systems.

- Low‑power family architecture Built on a low‑power process and device‑level optimizations that help reduce static power consumption in battery‑sensitive or thermally constrained applications.

- Power and operating conditions Core supply range 1.15 V to 1.25 V and commercial operating temperature 0 °C to 85 °C for standard electronics environments.

- Package and mounting 780‑FBGA (29 × 29) ball‑grid array, surface‑mount package for compact board integration and automated assembly.

- Regulatory status RoHS compliant, supporting environmentally responsible product builds.

Typical Applications

- Embedded control and interface hubs Use the device’s logic density and high I/O count to consolidate control, protocol bridging, and signal multiplexing in mid‑range embedded systems.

- Communications and networking On‑chip memory and abundant I/O make it suitable for packet buffering, PHY interface glue logic, and protocol adaptation in networking equipment.

- Consumer and handheld electronics Low‑power family architecture enables longer battery life and reduced thermal management for portable or hand‑held devices.

- Industrial automation Leverage flexible I/O and programmable logic to implement sensor aggregation, motor control interfaces, and custom timing logic for automation subsystems.

Unique Advantages

- Substantial programmable logic: The 81,264 logic elements provide the headroom to implement complex state machines, datapaths, and custom accelerators without external ASICs.

- Integrated memory resources: Approximately 2.8 Mbits of embedded RAM reduce dependence on external memory and simplify PCB routing and bill of materials.

- High I/O density: 429 I/Os enable direct connections to multiple peripherals and high‑pin‑count interfaces, reducing the need for external multiplexers or bridges.

- Compact system footprint: The 780‑FBGA (29×29) surface‑mount package supports dense board layouts and automated assembly workflows.

- Energy‑aware architecture: Family‑level low‑power design choices help meet thermal and power budgets in portable and thermally constrained applications.

- Environmentally compliant: RoHS compliance supports designs aimed at global markets with environmental regulatory requirements.

Why Choose EP3C80F780C7N?

The EP3C80F780C7N combines mid‑range logic density with significant on‑chip RAM and a high I/O count in a compact 780‑BGA package, making it a practical choice for designers who need integration, flexible interfacing, and power‑aware operation. As a member of the Cyclone III family, it benefits from device‑level low‑power optimizations and a suite of system integration features that simplify clock management and on‑chip processing.

This device is well suited for engineering teams building cost‑sensitive, high‑functionality systems—providing a balance of capacity, I/O flexibility, and environmental compliance that supports scalable, long‑life product designs.

Request a quote or submit a sales inquiry to evaluate how the EP3C80F780C7N can fit your next design. Provide your quantity and delivery requirements for a tailored response.

Date Founded: 1968

Headquarters: Santa Clara, California, USA

Employees: 130,000+

Revenue: $54.23 Billion

Certifications and Memberships: ISO9001:2015, ISO14001:2015, ISO17025:2017, ISO27001:2022, ISO45001:2018, ISO50001:2018