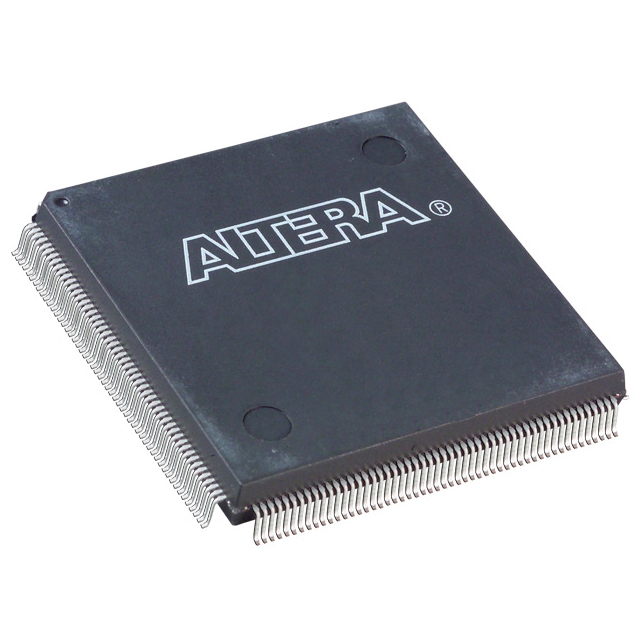

EPF6024AQC208-1

| Part Description |

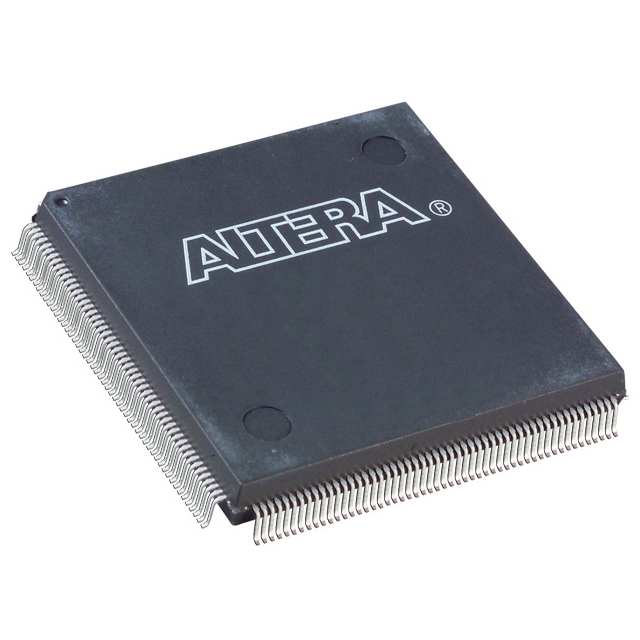

FLEX 6000 Field Programmable Gate Array (FPGA) IC 171 1960 208-BFQFP |

|---|---|

| Quantity | 431 Available (as of May 5, 2026) |

| Product Category | Field Programmable Gate Array (FPGA) |

|---|---|

| Manufacturer | Intel |

| Manufacturing Status | Obsolete |

| Manufacturer Standard Lead Time | RFQ |

| Datasheet |

Specifications & Environmental

| Device Package | 208-PQFP (28x28) | Grade | Commercial | Operating Temperature | 0°C – 85°C | ||

|---|---|---|---|---|---|---|---|

| Package / Case | 208-BFQFP | Number of I/O | 171 | Voltage | 3 V - 3.6 V | ||

| Mounting Method | Surface Mount | RoHS Compliance | Unknown | REACH Compliance | REACH Unaffected | ||

| Moisture Sensitivity Level | 3 (168 Hours) | Number of LABs/CLBs | 196 | Number of Logic Elements/Cells | 1960 | ||

| Number of Gates | 24000 | ECCN | 3A001A2A | HTS Code | 8542.39.0001 | ||

| Qualification | N/A |

Overview of EPF6024AQC208-1 – FLEX 6000 FPGA, 1,960 logic elements, 171 I/Os, 208-BFQFP

The EPF6024AQC208-1 is a FLEX 6000 family Field Programmable Gate Array from Intel, offering a programmable, register-rich LUT architecture built on the OptiFLEX design. With 1,960 logic elements and up to 24,000 typical gates, this device targets low-cost gate-array replacement, rapid prototyping and design testing, and in-system reconfigurable logic where flexible I/O and predictable timing matter.

Packaged in a 208-pin BFQFP surface-mount package and rated for commercial operation (0 °C to 85 °C) with a 3.0 V to 3.6 V supply range, the EPF6024AQC208-1 provides a balance of density, I/O count (171 pins), and configuration flexibility for embedded and system-level designs.

Key Features

- Core architecture — Register-rich, LUT-based OptiFLEX architecture that optimizes device area efficiency and supports fast design changes during prototyping and design testing.

- Logic density — 1,960 logic elements providing approximately 24,000 typical gates for implementing mid-density logic functions.

- I/O capability — 171 I/O pins with MultiVolt I/O interface support; features include individual tri-state output enable control, programmable output slew-rate control, and a fast register-to-pin path for improved clock-to-output timing.

- Reconfigurability & configuration — In-circuit reconfigurability (ICR) via external configuration device or intelligent controller, enabling field updates and iterative design revisions.

- Clocking and routing — Built-in low-skew clock distribution tree and four low-skew global paths; FastTrack continuous routing structure plus dedicated carry and cascade chains for efficient arithmetic and high-fan-in logic.

- Testability — Built-in JTAG boundary-scan (IEEE Std. 1149.1) circuitry available without consuming device logic, simplifying board-level test and debug.

- Package & mounting — 208-pin BFQFP (supplier package listed as 208-PQFP, 28×28) in a surface-mount form factor suited for compact PCBs.

- Power & compliance — Operates from 3.0 V to 3.6 V; low-power standby behavior is supported by the FLEX 6000 family. RoHS-compliant.

Typical Applications

- Prototyping and design validation — Rapid, reprogrammable logic lets teams iterate hardware functionality quickly during development and pre-production testing.

- Gate-array replacement — Cost-effective alternative to low-volume gate arrays where mid-range logic density and pin counts are required.

- System-level I/O bridging — MultiVolt I/O and extensive pin count support voltage-domain interfacing and peripheral glue logic across subsystems.

- Field-upgradeable logic — In-circuit reconfigurability enables in-field updates and feature revisions without PCB or silicon changes.

Unique Advantages

- Flexible reconfiguration: In-circuit reconfigurability via external devices or controllers simplifies firmware-driven feature updates and iterative development.

- Predictable timing and routing: Low-skew clock tree, four global paths, and FastTrack interconnect give designers clearer timing margins for synchronous designs.

- High I/O versatility: 171 I/Os with individual tri-state and programmable slew-rate controls allow optimized signal integrity and interfacing across peripherals.

- Built-in test support: Integrated IEEE 1149.1 JTAG boundary-scan reduces the need for additional test logic and eases board-level validation.

- Package density: 208-pin surface-mount BFQFP (208-PQFP, 28×28) offers a compact footprint while maintaining ample I/O for complex system integration.

Why Choose EPF6024AQC208-1?

The EPF6024AQC208-1 combines the FLEX 6000 family’s OptiFLEX architecture with 1,960 logic elements and 171 I/Os to deliver a mid-density, reprogrammable solution for designers who need adaptable logic and robust I/O in a compact package. Its support for in-circuit reconfiguration, dedicated arithmetic/cascade chains, and built-in boundary-scan make it suitable for iterative product development and systems that require post-deployment updates.

As a commercial-grade, RoHS-compliant device rated for 0 °C to 85 °C and operating from a 3.0 V to 3.6 V supply, the EPF6024AQC208-1 is positioned for embedded and system applications where flexibility, testability, and predictable routing are priorities.

Request a quote or submit an inquiry to check availability and pricing for the EPF6024AQC208-1 and to discuss how it can fit into your next design.

Date Founded: 1968

Headquarters: Santa Clara, California, USA

Employees: 130,000+

Revenue: $54.23 Billion

Certifications and Memberships: ISO9001:2015, ISO14001:2015, ISO17025:2017, ISO27001:2022, ISO45001:2018, ISO50001:2018