XCV50-5PQ240C

| Part Description |

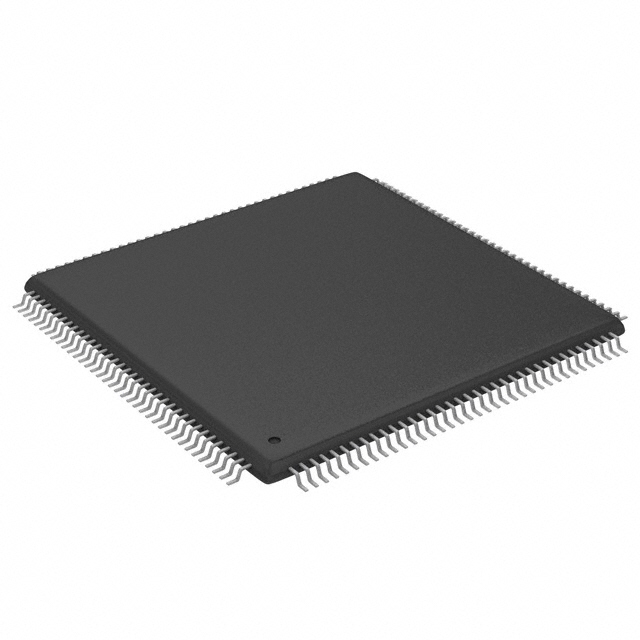

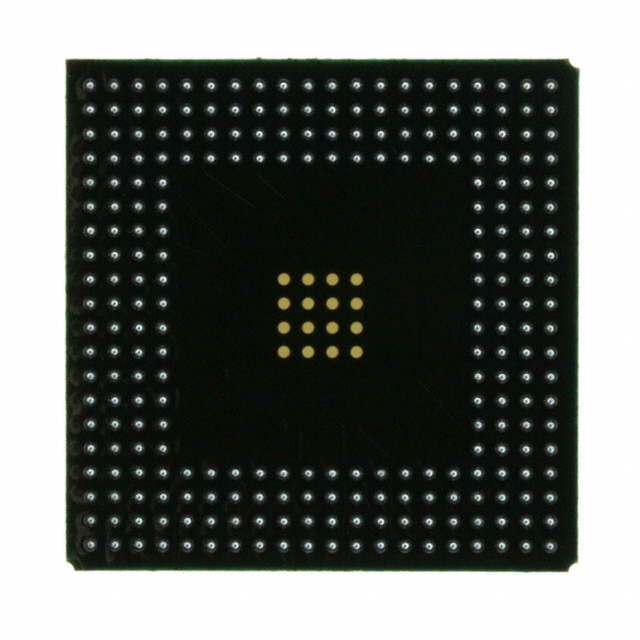

Virtex® Field Programmable Gate Array (FPGA) IC 166 32768 1728 240-BFQFP |

|---|---|

| Quantity | 1,467 Available (as of May 5, 2026) |

| Product Category | Field Programmable Gate Array (FPGA) |

|---|---|

| Manufacturer | AMD |

| Manufacturing Status | Obsolete |

| Manufacturer Standard Lead Time | RFQ |

| Datasheet |

Specifications & Environmental

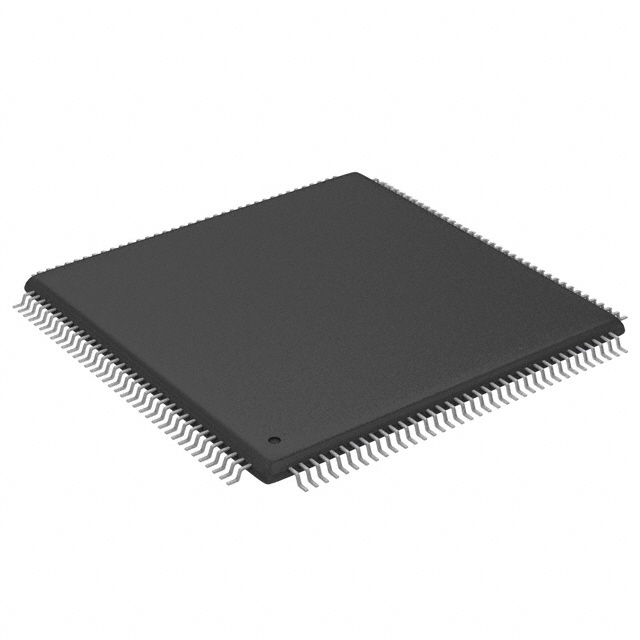

| Device Package | 240-PQFP (32x32) | Grade | Commercial | Operating Temperature | 0°C – 85°C | ||

|---|---|---|---|---|---|---|---|

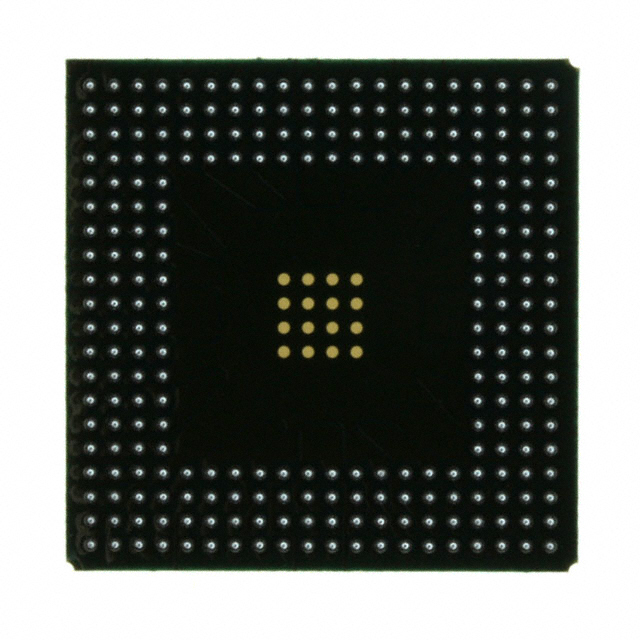

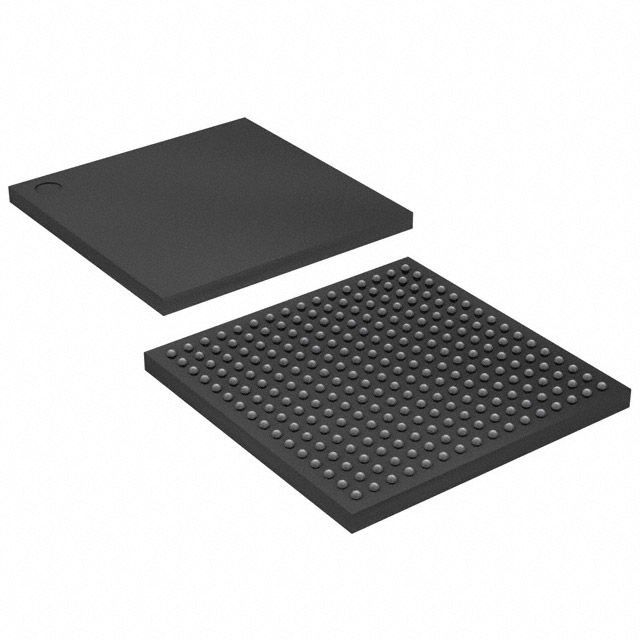

| Package / Case | 240-BFQFP | Number of I/O | 166 | Voltage | 2.375 V - 2.625 V | ||

| Mounting Method | Surface Mount | RoHS Compliance | RoHS non-compliant | REACH Compliance | REACH Unaffected | ||

| Moisture Sensitivity Level | 3 (168 Hours) | Number of LABs/CLBs | 384 | Number of Logic Elements/Cells | 1728 | ||

| Number of Gates | 57906 | ECCN | EAR99 | HTS Code | 8542.39.0001 | ||

| Qualification | N/A | Total RAM Bits | 32768 |

Overview of XCV50-5PQ240C – Virtex® Field Programmable Gate Array (FPGA) IC, 166 I/O, 1728 logic elements, 240-BFQFP

The XCV50-5PQ240C is an AMD (Xilinx) Virtex SRAM-based FPGA packaged in a 240-BFQFP surface-mount footprint. It delivers 1,728 logic elements, approximately 57,906 system gates, and 32,768 bits of on-chip RAM in a compact 240-pin PQFP (32 × 32) package.

Built on the Virtex family architecture, this commercial-grade device supports multi-standard I/O and advanced clock management, and is specified for a 2.375 V to 2.625 V supply and 0 °C to 85 °C operation—making it suitable for high-performance programmable-logic tasks including PCI-compliant applications and CompactPCI hot-swap designs.

Key Features

- Logic Capacity 1,728 logic elements (as specified) and approximately 57,906 system gates provide a compact, reprogrammable logic resource for control, glue logic, and custom datapath implementations.

- Embedded Memory 32,768 total RAM bits of on-chip memory with a hierarchical memory architecture; lookup tables (LUTs) are configurable for RAM or shift-register functions.

- I/O and Interfaces 166 I/O pins and Virtex family SelectIO™ support for multiple high-performance interface standards and direct connection to compatible external memory devices.

- Clock Management Built-in clock-management circuitry includes multiple delay-locked loops (DLLs), four primary low-skew global clock distribution nets, and additional secondary clock nets for flexible timing architectures.

- Arithmetic and DSP Support Dedicated carry logic and multiplier support enable efficient implementation of arithmetic and DSP functions.

- SRAM-Based In-System Configuration SRAM-based architecture provides unlimited re-programmability with multiple programming modes for in-system updates and design iteration.

- Package and Mounting 240-BFQFP (supplier package: 240-PQFP, 32×32) surface-mount package for compact board-level integration.

- Power and Environmental Core supply voltage range of 2.375 V to 2.625 V, commercial-grade operation from 0 °C to 85 °C, and RoHS compliance.

- Manufacturing and Test Virtex family devices are 100% factory tested as part of the product specification.

Typical Applications

- PCI and CompactPCI Systems Use the device in PCI-compliant interface logic and CompactPCI designs where 66-MHz PCI compatibility and hot-swap capability are required by the system architecture.

- Custom Interface and Bridge Logic Implement protocol bridging, bus interfacing, and glue logic with the device’s multi-standard SelectIO and abundant I/O resources.

- Embedded Control and Signal Processing Leverage dedicated multipliers, carry logic, and on-chip RAM for compact custom DSP, control loops, and real-time processing functions.

- In-System Programmable Prototyping Take advantage of SRAM-based, reprogrammable configuration to iterate hardware designs and validate algorithms in-system.

Unique Advantages

- Compact, reprogrammable logic: Provides 1,728 logic elements in a single 240-pin PQFP package, enabling dense functionality in a small footprint.

- Integrated memory resources: 32,768 bits of embedded RAM support buffering, FIFOs, and small local data stores without external memory.

- Flexible I/O standards: Multi-standard SelectIO capability and 166 available I/O pins simplify interfacing to a wide range of peripherals and memories.

- Robust clocking options: Multiple DLLs and global/local clock nets make it easier to implement precise timing and low-skew clock domains.

- Commercial-grade, RoHS-compliant: Specified for 0 °C to 85 °C operation with RoHS compliance for standard commercial applications.

Why Choose XCV50-5PQ240C?

The XCV50-5PQ240C positions itself as a compact, reprogrammable solution for designers who need moderate logic capacity, embedded RAM, and flexible I/O in a commercial-grade FPGA. Its Virtex-family architecture brings hierarchical memory, clock management, and dedicated arithmetic support into a surface-mount 240-BFQFP package suitable for space-constrained boards.

This device is appropriate for teams implementing PCI/CompactPCI interfaces, custom datapath and control logic, or in-system programmable prototypes where iterative development and integration flexibility are important. Its combination of on-chip resources and family-proven architecture supports scalable design reuse within Virtex-based development flows.

Request a quote or submit an inquiry for pricing and availability of the XCV50-5PQ240C to review lead times and order options.

Date Founded: 1969

Headquarters: Santa Clara, California, USA

Employees: 25,000+

Revenue: $22.68 Billion

Certifications and Memberships: ISO9001:2015, RoHS, REACH