XCV50-5TQ144C

| Part Description |

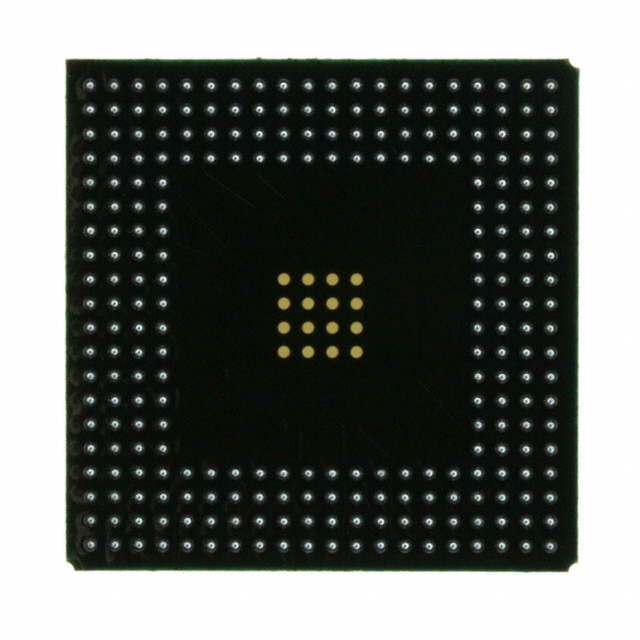

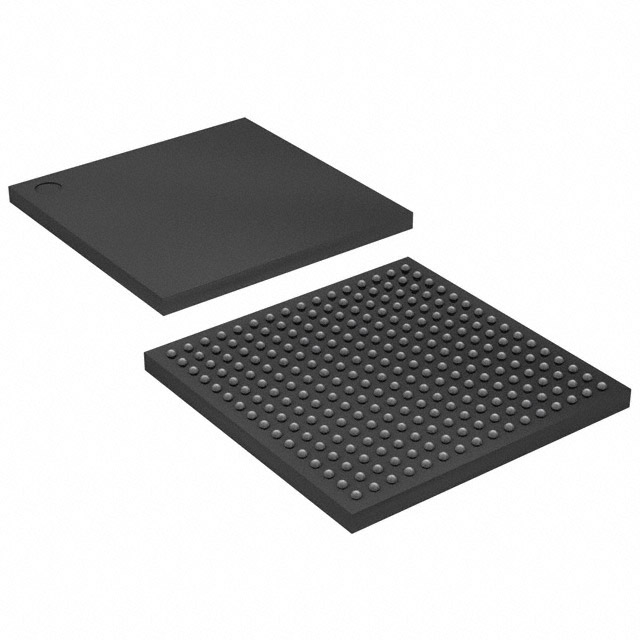

Virtex® Field Programmable Gate Array (FPGA) IC 98 32768 1728 144-LQFP |

|---|---|

| Quantity | 1,140 Available (as of May 5, 2026) |

| Product Category | Field Programmable Gate Array (FPGA) |

|---|---|

| Manufacturer | AMD |

| Manufacturing Status | Obsolete |

| Manufacturer Standard Lead Time | RFQ |

| Datasheet |

Specifications & Environmental

| Device Package | 144-TQFP (20x20) | Grade | Commercial | Operating Temperature | 0°C – 85°C | ||

|---|---|---|---|---|---|---|---|

| Package / Case | 144-LQFP | Number of I/O | 98 | Voltage | 2.375 V - 2.625 V | ||

| Mounting Method | Surface Mount | RoHS Compliance | RoHS non-compliant | REACH Compliance | REACH Unaffected | ||

| Moisture Sensitivity Level | 3 (168 Hours) | Number of LABs/CLBs | 384 | Number of Logic Elements/Cells | 1728 | ||

| Number of Gates | 57906 | ECCN | EAR99 | HTS Code | 8542.39.0001 | ||

| Qualification | N/A | Total RAM Bits | 32768 |

Overview of XCV50-5TQ144C – Virtex® FPGA, 1,728 logic elements, 32 Kbit embedded RAM, 144-LQFP

The XCV50-5TQ144C is an AMD Virtex® SRAM-based Field Programmable Gate Array (FPGA) in a 144-LQFP surface-mount package. It combines a regular CLB-based architecture with on-chip memory and dedicated clock-management resources to support reprogrammable logic implementations for embedded systems, prototyping, and interface bridging.

Designed for applications that require reconfigurable logic, flexible I/O and onboard RAM, this device offers a balance of logic density, I/O count and system-level features while operating at a core supply range of 2.375 V to 2.625 V and a commercial temperature rating of 0 °C to 85 °C.

Key Features

- Logic Resources — 384 configurable logic blocks (CLBs) providing 1,728 logic elements suitable for implementing custom digital functions and moderate-density designs.

- On-Chip Memory — Approximately 32,768 bits of embedded RAM for implementing lookup tables, small buffering, and on-chip data storage.

- System Gates — Approximately 57,906 system gates for estimating overall design capacity.

- I/O Capability — 98 user I/O pins to interface with external peripherals and memory devices in a wide range of system topologies.

- Clock Management — Four dedicated delay-locked loops (DLLs) with four primary low‑skew global clock nets plus 24 secondary local clock nets to support advanced clock control and distribution.

- Arithmetic and Routing — Dedicated carry logic and multiplier support along with a rich hierarchy of routing resources for high-speed arithmetic and complex interconnects (as described in the Virtex family specification).

- Packaging and Mounting — 144-LQFP (surface-mount) package, supplier package 144-TQFP (20×20), suitable for standard PCB assembly processes.

- Power and Temperature — Core voltage supply from 2.375 V to 2.625 V; commercial operating range from 0 °C to 85 °C.

- SRAM-Based Reconfigurability — SRAM configuration with multiple programming modes and unlimited reprogramming capability as part of the Virtex family architecture.

- Compliance — RoHS compliant.

Typical Applications

- Embedded system prototyping — Implement and iterate custom digital logic or system prototypes using the device’s reprogrammable fabric and on-chip RAM.

- Custom I/O bridging and interface control — Use the 98 I/Os and configurable logic to create protocol bridges, peripheral controllers or interface adaptors.

- DSP and arithmetic accelerators — Leverage dedicated carry logic, multiplier support and abundant registers for moderate-performance signal processing blocks.

- Compact PCI or bus-based modules — The Virtex family feature set includes PCI compliance and support for hot-swappable Compact PCI implementations as described in the product specification.

Unique Advantages

- Reprogrammable system flexibility: SRAM-based configuration enables in-system updates and multiple programming modes for iterative development and field updates.

- Balanced resource mix: 1,728 logic elements, 32 Kbit of on-chip RAM and 98 I/Os provide a practical combination of capacity and connectivity for mid-range designs.

- Integrated clock control: Four DLLs and hierarchical clock nets simplify clock management across complex logic partitions, improving timing predictability.

- Vendor-supported development: Supported by the Virtex family development systems and libraries, facilitating design integration and toolchain support.

- Industry-standard packaging: 144-LQFP surface-mount package fits standard assembly flows and simplifies prototype through production board layouts.

Why Choose XCV50-5TQ144C?

The XCV50-5TQ144C offers a compact, reprogrammable FPGA solution that balances logic density, on-chip memory and I/O for embedded and interface-focused designs. Its Virtex architecture provides dedicated arithmetic resources, flexible routing and integrated clock-management features to accelerate implementation of custom digital functions while retaining the ability to iterate designs in-system.

This device is appropriate for engineers and teams seeking a commercially graded, RoHS-compliant FPGA platform with a proven development ecosystem for prototyping, custom I/O control, DSP acceleration and bus-interface applications.

Request a quote or submit a procurement inquiry to get pricing and availability information for the XCV50-5TQ144C.

Date Founded: 1969

Headquarters: Santa Clara, California, USA

Employees: 25,000+

Revenue: $22.68 Billion

Certifications and Memberships: ISO9001:2015, RoHS, REACH