XCV600E-8BG432C

| Part Description |

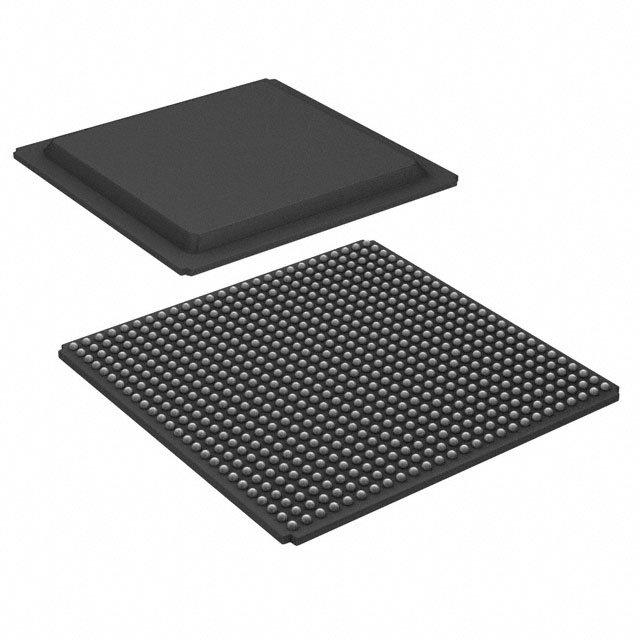

Virtex®-E Field Programmable Gate Array (FPGA) IC 316 294912 15552 432-LBGA Exposed Pad, Metal |

|---|---|

| Quantity | 1,400 Available (as of May 5, 2026) |

| Product Category | Field Programmable Gate Array (FPGA) |

|---|---|

| Manufacturer | AMD |

| Manufacturing Status | Obsolete |

| Manufacturer Standard Lead Time | RFQ |

| Datasheet |

Specifications & Environmental

| Device Package | 432-MBGA (40x40) | Grade | Commercial | Operating Temperature | 0°C – 85°C | ||

|---|---|---|---|---|---|---|---|

| Package / Case | 432-LBGA Exposed Pad, Metal | Number of I/O | 316 | Voltage | 1.71 V - 1.89 V | ||

| Mounting Method | Surface Mount | RoHS Compliance | RoHS non-compliant | REACH Compliance | REACH Unaffected | ||

| Moisture Sensitivity Level | 3 (168 Hours) | Number of LABs/CLBs | 3456 | Number of Logic Elements/Cells | 15552 | ||

| Number of Gates | 985882 | ECCN | 3A991D | HTS Code | 8542.39.0001 | ||

| Qualification | N/A | Total RAM Bits | 294912 |

Overview of XCV600E-8BG432C – Virtex®-E FPGA, 432-LBGA, 15,552 logic elements

The XCV600E-8BG432C is a Virtex®-E family field programmable gate array (FPGA) in a 432-LBGA exposed pad metal package. It combines programmable logic, embedded RAM, and high-density I/O to support reconfigurable system designs.

Targeted at applications that require flexible, reprogrammable logic and high-performance interfaces, this commercial-grade device offers on-chip memory, abundant I/O, and SRAM-based in-system configuration for iterative development and deployment.

Key Features

- Core and logic Provides 15,552 logic elements and approximately 985,882 gates for implementing complex digital functions.

- Embedded memory Total on-chip RAM is 294,912 bits (approximately 0.295 Mbits) to support local buffering and intermediate storage.

- I/O capacity and signaling (family feature) Device offers 316 user I/O pins; the Virtex‑E family supports a wide range of high-performance and differential I/O standards.

- Clock management (family feature) Built on Virtex‑E architecture which includes advanced clock management circuitry, including multiple digitally controlled DLLs for clocking flexibility.

- SRAM-based in-system configuration Supports reprogrammability via SRAM-based configuration for in-system updates and design iteration.

- Power and supply Operates with a core voltage supply range of 1.71 V to 1.89 V; internal logic supply centered on the Virtex‑E family nominal 1.8 V.

- Package and mounting Supplied in a 432-LBGA exposed pad, metal package (supplier package: 432-MBGA, 40×40) for surface-mount assembly; RoHS compliant.

- Commercial temperature grade Rated for operation from 0 °C to 85 °C to meet commercial embedded system requirements.

Typical Applications

- PCI-based systems Suitable for integration into PCI-compliant 3.3 V, 32/64-bit, 33/66-MHz system interfaces referenced in the Virtex‑E feature set.

- Memory interface and controllers Designed to support high-performance external memory interfaces and DDR/SDRAM topologies as described for the Virtex‑E family.

- High-speed data acquisition and processing Combines dense logic and on-chip RAM with extensive I/O to implement front-end data capture, buffering, and preprocessing.

- Reconfigurable system prototyping SRAM-based in-system programmability enables iterative hardware development and field updates without replacing components.

Unique Advantages

- High logic density: 15,552 logic elements and nearly one million gates provide capacity for substantial digital functionality on a single device.

- On-chip memory availability: Approximately 0.295 Mbits of embedded RAM reduce dependence on external memory for many intermediate storage needs.

- Extensive I/O: 316 I/O pins and the Virtex‑E family’s support for multiple differential signaling standards enable flexible interfacing to modern peripherals.

- Reprogrammable architecture: SRAM-based in-system configuration enables design updates and iterative optimization without hardware changes.

- Commercial-grade reliability: Rated for 0 °C to 85 °C operation and packaged in a rugged 432-LBGA exposed pad metal package suitable for standard board assembly processes.

Why Choose XCV600E-8BG432C?

The XCV600E-8BG432C positions itself as a versatile, reprogrammable FPGA for designs that need a balance of logic capacity, embedded RAM, and flexible I/O in a compact surface-mount package. Its Virtex‑E architecture delivers the family-level clocking, I/O, and memory features that support demanding interface and embedded-system requirements.

This device is well suited for development teams and OEMs implementing PCI-compliant systems, memory interface controllers, or data acquisition front ends who need a commercially rated FPGA with field-update capability and a high density of logic resources.

Request a quote or submit an RFQ today to obtain pricing and availability for the XCV600E-8BG432C.

Date Founded: 1969

Headquarters: Santa Clara, California, USA

Employees: 25,000+

Revenue: $22.68 Billion

Certifications and Memberships: ISO9001:2015, RoHS, REACH