1SG280HH3F55E1VG

| Part Description |

Stratix® 10 GX Field Programmable Gate Array (FPGA) IC 1160 2800000 2912-BBGA, FCBGA |

|---|---|

| Quantity | 547 Available (as of May 5, 2026) |

| Product Category | Field Programmable Gate Array (FPGA) |

|---|---|

| Manufacturer | Intel |

| Manufacturing Status | Active |

| Manufacturer Standard Lead Time | 12 Weeks |

| Datasheet |

Specifications & Environmental

| Device Package | 2912-FBGA, FC (55x55) | Grade | Extended | Operating Temperature | 0°C – 100°C | ||

|---|---|---|---|---|---|---|---|

| Package / Case | 2912-BBGA, FCBGA | Number of I/O | 1160 | Voltage | 770 mV - 970 mV | ||

| Mounting Method | Surface Mount | RoHS Compliance | Unknown | REACH Compliance | REACH Unaffected | ||

| Moisture Sensitivity Level | 3 (168 Hours) | Number of LABs/CLBs | 350000 | Number of Logic Elements/Cells | 2800000 | ||

| Number of Gates | N/A | ECCN | N/A | HTS Code | N/A | ||

| Qualification | N/A | Total RAM Bits | 240123904 |

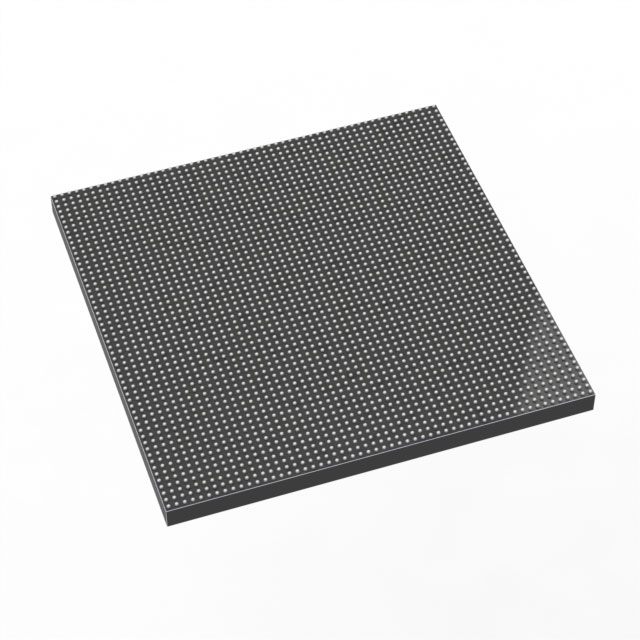

Overview of 1SG280HH3F55E1VG – Stratix® 10 GX Field Programmable Gate Array (FPGA), 2,800,000 logic elements, 1160 I/O

The 1SG280HH3F55E1VG is a Stratix® 10 GX FPGA in a 2912-BBGA FCBGA package designed for high-performance programmable logic applications. As part of the Stratix 10 GX family, the device leverages the Intel Hyperflex core architecture and Intel 14 nm tri-gate (FinFET) technology to address demanding bandwidth and processing requirements.

This device is suited for applications that require large programmable fabric, substantial on-chip RAM, and dense I/O—for example, advanced networking, data center acceleration, and communications infrastructure—while providing extended-grade operating range and RoHS compliance.

Key Features

- Logic Capacity 2,800,000 logic elements to implement large-scale custom logic, protocol stacks, and compute pipelines.

- Fabric Architecture Part of the Stratix 10 GX family featuring the Intel Hyperflex core architecture and Intel 14 nm tri-gate (FinFET) technology for improved core performance and power efficiency (series-level characteristics).

- On-chip Memory 240,123,904 total RAM bits for buffering, packet processing, and stateful algorithms.

- I/O Density 1,160 I/O pins to support dense board-level interfaces and multiple high-speed links.

- Package & Mounting 2912-BBGA, FCBGA package (supplier device package: 2912-FBGA, FC, 55×55) with surface-mount construction for high-density PCB integration.

- Supply Voltage Operating core voltage range of 770 mV to 970 mV to match system power domains and regulator designs.

- Operating Range Extended grade with an operating temperature range of 0 °C to 100 °C suitable for controlled-environment and data center deployments.

- Standards & Compliance RoHS compliant.

- Family-Level I/O & Transceiver Capabilities Stratix 10 GX family innovations include heterogeneous 3D SiP transceiver tiles and high-speed transceiver channels (series-level features described in family documentation).

Typical Applications

- High‑Performance Networking: Implement packet processing, forwarding engines, and line-rate protocol logic using the device’s large logic capacity and dense I/O.

- Data Center Acceleration: Deploy custom compute accelerators and hardware offload functions that leverage substantial on-chip RAM and large programmable fabric.

- Telecommunications Infrastructure: Support multi‑lane, high-speed links and complex FEC or PHY implementations using family-level transceiver resources and hard IP available in the Stratix 10 GX series.

- High‑Bandwidth Digital Systems: Integrate protocol bridging, routing, or custom DSP logic where high I/O count and large memory arrays are required.

Unique Advantages

- Large Programmable Fabric: 2.8 million logic elements provide room to implement complex state machines, pipelines, and custom accelerators without partitioning across multiple devices.

- Substantial On-Chip Memory: 240,123,904 bits of RAM reduce external memory dependence for buffering and stateful processing, simplifying board-level memory architecture.

- High I/O Count: 1,160 I/O pins support diverse interface mixes and high-density interconnects for multi-lane link topologies.

- Extended-Grade Operation: Rated for 0 °C to 100 °C operation for reliable performance in data center and telecom system environments.

- Packaging for Dense Boards: 2912-BBGA/2912-FBGA (55×55) package enables compact, high-density PCB layouts suitable for modern system designs.

- Compliant and Ready: RoHS compliance supports environmentally regulated manufacturing processes.

Why Choose 1SG280HH3F55E1VG?

The 1SG280HH3F55E1VG delivers the capacity and I/O density required for demanding programmable logic designs where large-scale custom logic, significant on-chip RAM, and many board-level interfaces are essential. As a Stratix 10 GX family device, it benefits from the family’s Hyperflex architecture and 14 nm FinFET technology, aligning performance and power considerations for advanced networking, data center, and telecom systems.

This device is well suited for engineering teams designing scalable, high-throughput systems that require extended-grade operation and compact board-level integration. Its combination of logic elements, memory, and I/O density provides a platform that can reduce external components and simplify system partitioning while leveraging the Stratix 10 family feature set described in the device documentation.

Request a quote or contact sales to discuss availability, volume pricing, or to submit your design requirements for this Stratix 10 GX FPGA.

Date Founded: 1968

Headquarters: Santa Clara, California, USA

Employees: 130,000+

Revenue: $54.23 Billion

Certifications and Memberships: ISO9001:2015, ISO14001:2015, ISO17025:2017, ISO27001:2022, ISO45001:2018, ISO50001:2018